Innovative Technology for Computer Professionals

**Multiprocessor**

Judging Science Fairs, p. 12

Timeliness in Networked Embedded Systems, p. 85

The Tech Buzz Game, p. 94

er

**July 2005**

July 2005, Volume 38, Number 7

Cover design and artwork by Dirk Hagner

### **ABOUT THIS ISSUE**

he emergence of application-specific integrated circuit and system-on-chip (SoC) manufacturing technologies in the 1990s laid the groundwork for a new era of post-RISC, configurable processors. Using the advanced development tools that are currently available, combined with the requisite softwaredevelopment tools for that architecture, developers can now tailor a microprocessor core for specific application tasks in minutes, a shockingly brief time relative to the time spent designing processors and their associated development tools in prior eras. In this issue, we look at a reconfigurable MPSoC emulation platform from STMicroelectronics, ARM's instruction set architecture, Tensilica's configurable processors, and EEMBC's DENBench suite of digital media benchmarks.

### COMPUTING PRACTICES

### Securing Wi-Fi Networks

*Kjell J. Hole, Erlend Dyrnes, and Per Thorsheim* Hackers can decrypt and read data on a wireless link protected by built-in WEP encryption, and they may even be able to access the data on a wired network through a Wi-Fi access point. The authors assess Wi-Fi network security in one city, analyze alternative security techniques, and suggest ways to secure such networks.

### **COVER FEATURES**

### **GUEST EDITORS' INTRODUCTION**

### Multiprocessor Systems-on-Chips

Ahmed Jerraya, Hannu Tenhunen, and Wayne Wolf Single processors may be sufficient for low-performance applications that are typical of early microcontrollers, but an increasing number of applications require multiprocessors to meet their performance goals.

### 42 Parallelism and the ARM Instruction Set Architecture

### John Goodacre and Andrew N. Sloss

Leveraging parallelism on several levels, ARM's new chip designs could change how people access technology. With sales growing rapidly and more than 1.5 billion ARM processors already being sold each year, software writers now have a huge range of markets in which their ARM code can be used.

### Configurable Processors: A New Era in Chip Design

### Steve Leibson and James Kim

51

Configurable processors can achieve much higher performance than processors with conventional fixed-instruction-set architectures through the addition of custom-tailored execution units, registers, and register files as well as communication interface ports.

### 60 An Open Platform for Developing Multiprocessor SoCs

Mario Diaz Nava, Patrick Blouet, Philippe Teninge, Marcello Coppola, Tarek Ben-Ismail, Samuel Picchiottino, and Robin Wilson A low-cost modular approach that uses emulation offers an alternative to software simulation for the design and verification of complex multiprocessor system-on-chip (MPSoC) designs.

### 68 Evaluating Digital Entertainment System Performance

### Markus Levy

The Embedded Microprocessor Benchmark Consortium's DENBench suite of digital media benchmarks provides a spectrum of tools for assessing and refining the video and audio performance of digital devices.

IEEE Computer Society: http://www.computer.org Computer: http://www.computer.org/computer computer@computer.org IEEE Computer Society Publications Office: +1 714 821 8380

## OPINION

At Random

Judging Science Fairs Bob Colwell

### N E W S

### **Industry Trends**

Eclipse Becomes the Dominant Java IDE *David Geer*

### Technology News

Instant Messaging: A New Target for Hackers *Neal Leavitt*

### **News Briefs**

Putting a Business Suit on Grid Technology Unusual Attack Holds Computer Files for Ransom Schools Increasingly Use Software to Grade Essays

### MEMBERSHIP NEWS

### **Call and Calendar**

### **Computer Society Connection**

### COLUMNS

### Embedded Computing

Absolutely Positively on Time: What Would It Take? *Edward A. Lee*

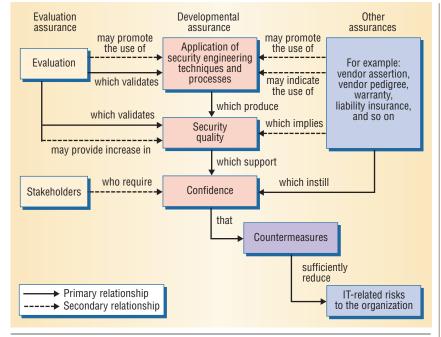

### Standards

Developer-Focused Assurance Requirements Gary Stoneburner

### IT Systems Perspectives

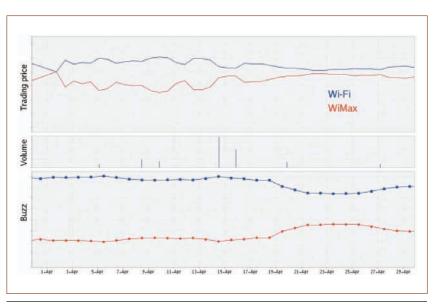

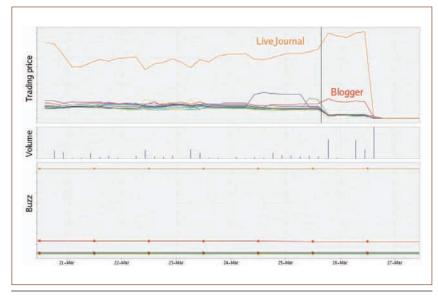

The Tech Buzz Game Bernard Mangold, Mike Dooley, Gary W. Flake, Havi Hoffman, Tejaswi Kasturi, David M. Pennock, and Rael Dornfest

NEXT

MONTH:

Ultimate Display

Technology

### The Profession

The Turning of the Wheel *Neville Holmes*

### DEPARTMENTS

Article Summaries Letters 32 & 16 Advertiser/Product Index Career Opportunities Products Bookshelf IEEE Computer Society Membership Application

of the

Editor in Chief Doris L. Carver Louisiana State University d.carver@computer.org

Associate Editors in Chief Bill N. Schilit Intel Kathleen Swigger University of North Texas

### Area Editors

Computer Architectures Douglas C. Burger University of Texas at Austin Databases/Software Michael R. Blaha OMT Associates Inc.

**Graphics and Multimedia** Oliver Bimber Bauhaus University Weimar

Information and Data Management Naren Ramakrishnan Virginia Tech

**Multimedia** Savitha Srinivasan IBM Almaden Research Center

Networking Jonathan Liu University of Florida

Software H. Dieter Rombach AG Software Engineering Dan Cooke Texas Tech University Computing Practices Rohit Kapur rohit.kapur@synopsys.com

Perspectives Bob Colwell bob.colwell@comcast.net

Research Features Kathleen Swigger kathy@cs.unt.edu

**Column Editors**

At Random

Bob Colwell

Michael J. Lutz

Rochester Institute of

Princeton University

**Embedded Computing**

**Entertainment Computing**

Georgia Tech Research Institute

Michael R. Macedonia

**IT Systems Perspectives**

Richard G. Mathieu

**Invisible Computing**

University of Tasmania

University of Maryland

St. Louis University

Bill N. Schilit

The Profession

Neville Holmes

Bill Arbaugh

Intel

Security

Bookshelf

Technology

Wayne Wolf

Special Issues Bill Schilit schilit@computer.org

Web Editor Ron Vetter vetterr@uncw.edu

Standards

Jack Cole

US Army Research Laboratory

Web Technologies

San Jose State University

**Advisory Panel**

University of Virginia

University of Pittsburgh

University of Pittsburgh

Edward A. Parrish

University of Virginia

Semiconductor Research Corp.

Worcester Polytechnic Institute

University of North Carolina at

James H. Aylor

Thomas Cain

Ralph Cavin

Ron Vetter

Wilmington

Alf Weaver

Ron Hoelzeman

Simon S.Y. Shim

2005 IEEE Computer Society President Gerald L. Engel president@computer.org

### **CS** Publications Board

Michael R. Williams (chair), Michael R. Blaha, Roger U. Fujii, Sorel Reisman, Jon Rokne, Bill N. Schilit, Nigel Shadbolt, Linda Shafer, Steven L. Tanimoto, Anand Tripathi

### CS Magazine Operations Committee

Bill Schilit (chair), Jean Bacon, Pradip Bose, Doris L. Carver, Norman Chonacky, George Cybenko, John C. Dill, Frank E. Ferrante, Robert E. Filman, Forouzan Golshani, David Alan Grier, Rajesh Gupta, Warren Harrison, James Hendler, M. Satyanarayanan

### **Editorial Staff**

Scott Hamilton Senior Acquisitions Editor shamilton@computer.org Judith Prow Managing Editor jprow@computer.org James Sanders Senior Editor Lee Garber Senior News Editor Chris Nelson Associate Editor Mary-Louise G. Piner Staff Lead Editor Yu-Tzu Tsai Assistant Editor Bob Ward Membership News Editor Bryan Sallis Manuscript Assistant **Design** Larry Bauer Dirk Hagner **Production** Larry Bauer

### Administrative Staff

Executive Director David W. Hennage Publisher Angela Burgess aburgess@computer.org Assistant Publisher Dick Price Membership & Circulation Marketing Manager Georgann Carter Business Development Manager Sandy Brown Senior Advertising Coordinator Marian Anderson

Circulation: Computer (ISSN 0018-9162) is published monthly by the IEEE Computer Society. IEEE Headquarters, Three Park Avenue, 17th Floor, New York, NY 10016-5997; IEEE Computer Society Publications Office, 10662 Los Vaqueros Circle, PO Box 3014, Los Alamitos, CA 90720-1314; voice +1 714 821 8380; fax +1 714 821 4010; IEEE Computer Society Headquarters, 1730 Massachusetts Ave. NW, Washington, DC 20036-1903. IEEE Computer Society membership includes \$19 for a subscription to Computer magazine. Nonmember subscription rate available upon request. Single-copy prices: members \$20.00; nonmembers \$94.00.

Postmaster: Send undelivered copies and address changes to *Computer*, IEEE Membership Processing Dept., 445 Hoes Lane, Piscataway, NJ 08855. Periodicals Postage Paid at New York, New York, and at additional mailing offices. Canadian GST #125634188. Canada Post Corporation (Canadian distribution) publications mail agreement number 40013885. Return undeliverable Canadian addresses to PO Box 122, Niagara Falls, ON L2E 658 Canada. Printed in USA.

Editorial: Unless otherwise stated, bylined articles, as well as product and service descriptions, reflect the author's or firm's opinion. Inclusion in *Computer* does not necessarily constitute endorsement by the IEEE or the Computer Society. All submissions are subject to editing for style, clarity, and space.

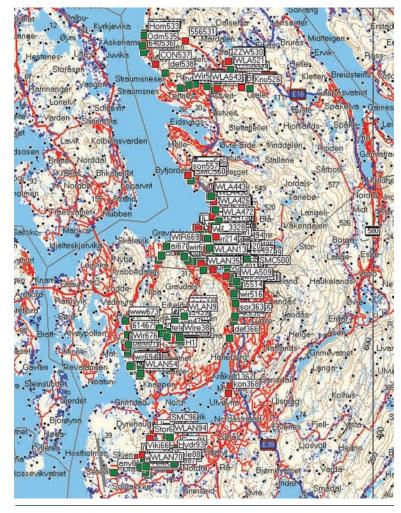

### Securing Wi-Fi Networks pp. 28-34

*Kjell J. Hole, Erlend Dyrnes, and Per Thorsheim*

s Wi-Fi networks have become increasingly popular, many corporations have added Wi-Fi access to give employees easier access to corporate data and services. Although IT personnel control Wi-Fi access points in the corporate network, they cannot control access points in home networks. These networks thus give hackers new opportunities to gain unauthorized access to corporate computer systems and their data.

The results of an investigation conducted to assess the security level in Wi-Fi networks in Bergen, Norway, provide a context for analyzing some popular wireless security techniques and for offering suggestions on how to better protect these networks from hacking.

### Parallelism and the ARM Instruction Set Architecture pp. 42-50

John Goodacre and Andrew N. Sloss

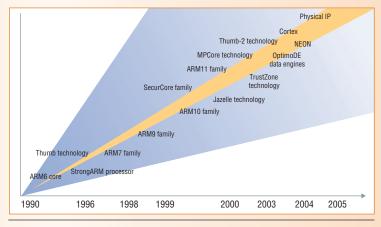

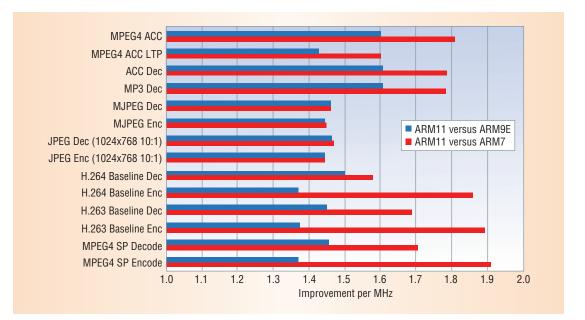

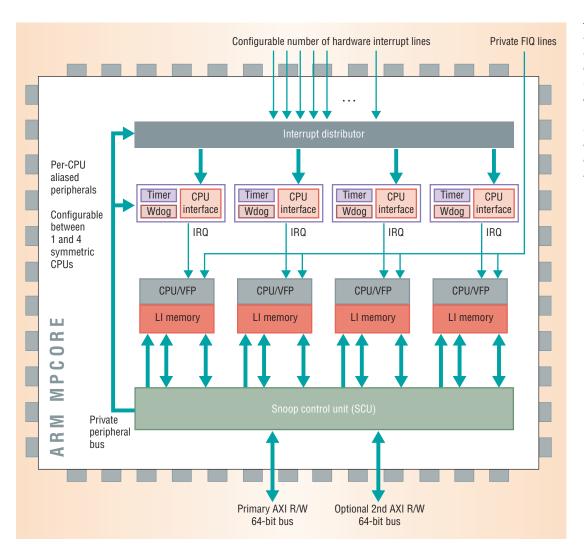

he ARM reduced-instruction-set computing processor has evolved to offer a family of chips that range up to a full-blown multiprocessor. Embedded applications' demand for increasing levels of performance and the added efficiency of key new technologies have driven the ARM architecture's evolution.

The ARM team has used the full range of computer architecture techniques for exploiting parallelism, including variable execution time, subword parallelism, DSP-like operations, thread-level parallelism and exception handling, and multiprocessing.

The ARM architecture's developmental history shows how processors have used different types of parallelism over time. With its foundation in low-power design, the new ARM11 MPCore multiprocessor can bring low power to high-performance designs, which show the potential to truly change how people access technology.

Computer

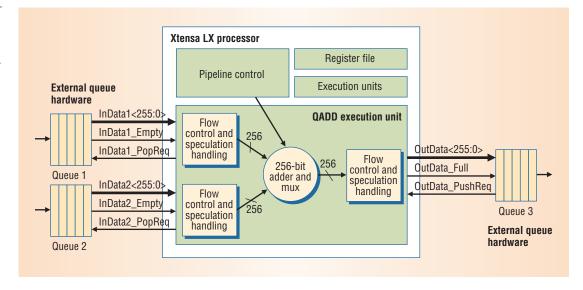

### Configurable Processors: A New Era in Chip Design pp. 51-59

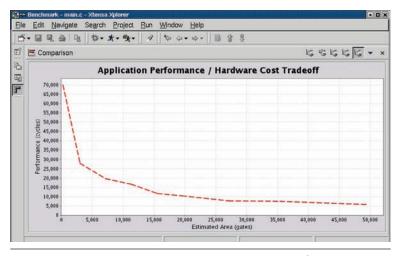

Steve Leibson and James Kim

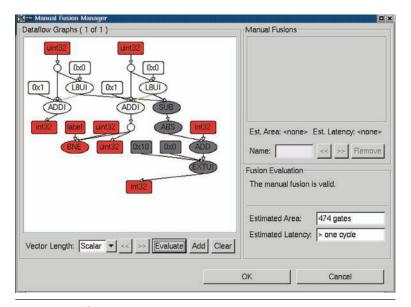

Designers can use advanced development tools to tailor a microprocessor core for specific application tasks and generate the processor's register-transfer-level description. They can also generate all the requisite software-development tools for that architecture in minutes. This entire process takes a shockingly brief time relative to the time spent designing processors and their associated development tools in prior eras.

With automated tools, designers can focus on system architectural issues to achieve performance goals rather than spending time designing individual functional blocks within the SoC.

The configurable processor represents the next evolutionary step in microprocessor development, paving the way for new and interesting architectures that employ multiple, heterogeneous processor cores and exploit the qualities of advanced semiconductor lithography.

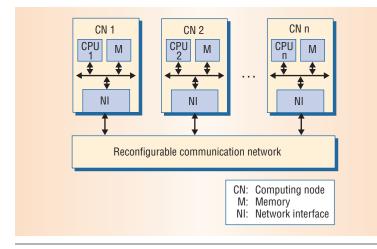

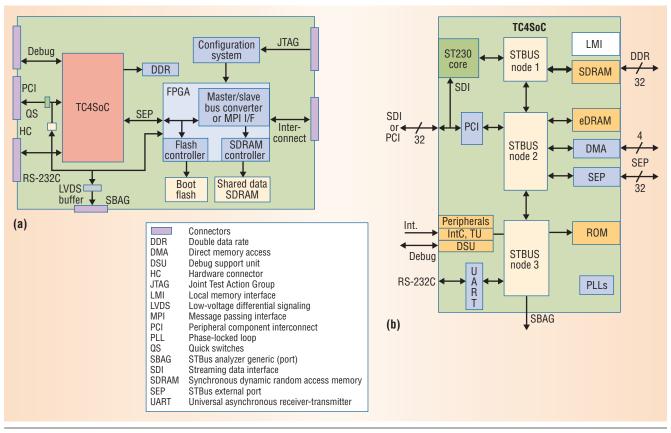

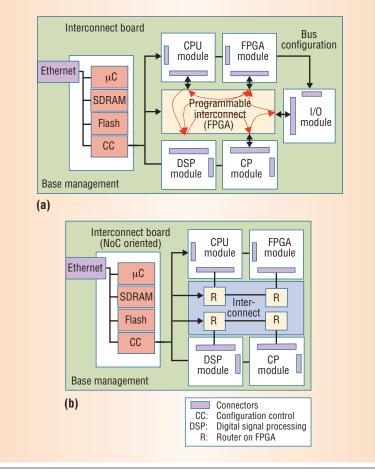

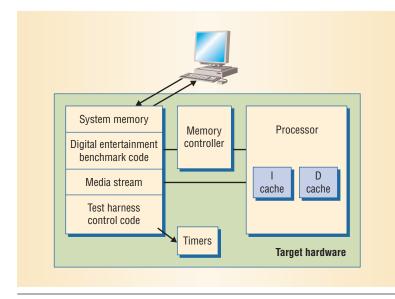

### An Open Platform for Developing Multiprocessor SoCs pp. 60-67

Mario Diaz Nava, Patrick Blouet, Philippe Teninge, Marcello Coppola, Tarek Ben-Ismail, Samuel Picchiottino, and Robin Wilson

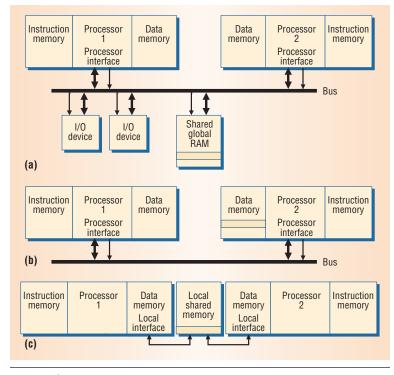

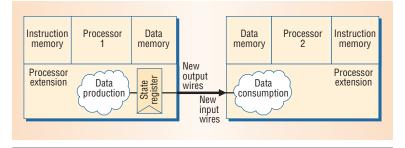

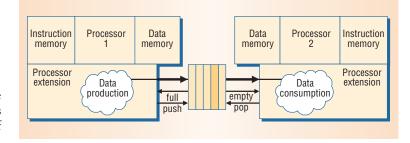

The opportunities that nanometer technologies provide, combined with the consolidation of platformbased design approaches, have driven the evolution toward multiprocessor architectures, and the network-on-chip paradigm suggests new methods for designing and verifying embedded systems.

Clearly, a pure software simulation platform can't provide the performance required for developing multiprocessor system-on-chip designs. What's more, a main design risk for today's systems is the architecture, which developers must validate early in the design cycle because it has the biggest impact on system dimensioning and performances.

The authors describe an approach that introduces concurrent hardware and software engineering early in the development process and uses low-cost emulation facilities. Their approach extends the emulation used for verifying application-specific integrated circuits and application-specific standard product devices to multiprocessor architectures. They plan to introduce this platform in consumer and telecommunications product development to increase software and hardware engineers' productivity, which will reduce development time and costs while ensuring design and product quality.

### Evaluating Digital Entertainment System Performance pp. 68-72

Markus Levy

D igital entertainment systems have become the driving force behind the expansion of the semiconductor market, outstripping even PCs. In 2003, for example, smart phones represented about 3 percent of the 500 million mobile phones sold worldwide, with analysts expecting their sales to grow at triple-digit year-over-year rates.

More than half of the 600 million mobile phones sold in 2004 included a color display and digital camera. The implementation of more advanced features such as accelerated 2D and 3D graphics, videoconferencing, mobile multimedia, and games has raised performance requirements. The same holds true for other digital entertainment devices.

Rapid advances in semiconductor technology, microarchitectures, and embedded systems have made the adoption of these features possible. As a result, software complexity will continue to increase to keep pace with overall system complexities.

Performance and quality provide good starting points for evaluating a digital entertainment system, but energy consumption is an equally important metric.

## **Call for Participation**

Attend the 21st International Conference on Software Maintenance (ICSM), the world's foremost conference for software and systems maintenance, evolution, and management. This conference looks back upon a 22 year history of cooperation between industry and research in solving the problems of sustaining and enhancing existing software systems. It combines research results with reports from the field and tool demonstrations. Topics range from source analysis and reverse engineering to maintenance process modeling and maintenance cost estimation.

Continuous Evolution is the theme. It emphasizes that complex software systems are never finished. Once they go into production, they enter a phase of continuous evolution, which carries on as long as there are new requirements to be fulfilled. The task of maintaining a system in production, at the same time renovating and enhancing it, has been compared to repairing and reengineering a plane in flight, at the same time lengthening the wings.

The ICSM conference will give you the chance to meet with professional colleagues from all over the world and to share your experience with them in a congenial atmosphere. You will be able to attend industrial sessions with reports on real life projects, to study at tutorials by experts on maintenance topics, to hear keynote speeches from renowned experts, to see tool demonstrations, to take part in panel sessions, and to listen in on the latest research reports.

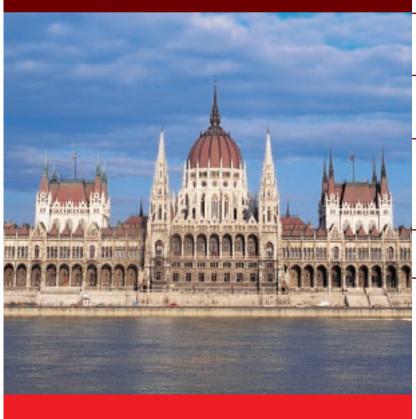

Don't miss this great opportunity to enhance your knowledge and enrich your skills, and to learn more about a country with a fascinating culture and an interesting past. A csardas evening in the wine cellars of the Buda hills and a trip to the puszta will be offered to conference attendees. The conference itself is located on an island in the Danube river between the twin cities of Buda and Pest.

# **International Conference** on Software Maintenance 2005

Budapest, Hungary, 26-29 September, 2005 www.inf.u-szeged.hu/icsm2005

REGISTER

**ONLINE AT:** http://www.inf.u-szeged.hu/icsm2005/

**BY EMAIL TO:** Cserep.andi@mail.gatesgroup.hu

**BY FAX TO:** #36-1-214-9316

### **IMPORTANT DEADLINES:**

Early Registration closes: Hotel rooms to be booked by:

### **CONFERENCE:**

Tutorials and Industrial Session: **Regular Conference:**

September 26, 2005 September 27-29, 2005

August 30, 2005

August 25, 2005

### **TUTORIALS:**

- "Developing Supportable Enterprise Information Systems" by Leszek Maciaszek

- "Using Metrics to improve Maintenance Testing" by Alfred Sorkowitz "Object-Oriented Reengineering - Patterns & Techniques"

- by Serge Demeyer, Stephane Ducasse & Oscar Nierstrasz

- "60 vears of Software Maintenance"

- by Nicholas Zvegintzov & Girish Parikh

### **KEYNOTES:**

Ian Sommerville on "Construction by configuration" Girish Parikh on "Software Support, Management and Evolution"

### **GENERAL CHAIR:**

Harry M. Sneed, ANECON GmbH, Vienna, Austria, Harry.Sneed@t-online.de

### PROGRAM CO-CHAIRS:

Tibor Gyimóthy, University of Szeged, Hungary, gyimi@inf.u-szeged.hu Vaclav Rajlich, Wayne State University, USA rajlich@cs.wayne.edu

The patron of the conference is E. Sylvester Vizi, President of Hungarian Acadamy of Sciences.

### **A PACKING LIST**

Before Bob Colwell sets out on his missionary work to explain engineering to the humanities community (At Random, "Frames of Reference," June 2005, pp. 9-11), he should include the following in his packing list:

- a book on reasoning,

- a history of the 20th century, and a subscription to the *Journal of*

- the History of Ideas.

The New Age mystic and the school board official that Colwell cites as representatives of the humanities are as abhorrent to those of us in the "difficult" sciences as they are to our colleagues in the "hard" sciences.

Colwell appeals to the common prejudice of technologists that the humanities have no standards, hence, anything goes. That appeal is furthered by an inadequate sample that would not pass muster in any technology discussion.

Is scientific illiteracy a problem? Undoubtedly, but then so is humanities illiteracy. What else would explain representatives of the hard sciences writing claptrap like the Bible Code books? It is not good science, much less good humanities work.

But it would be unfair, not to mention inaccurate, to characterize all technologists on the basis of a few carefully chosen examples.

Colwell's claim in his conclusion that people in the technology business must realize they are "in the service of truth, an absolute truth that must be guarded" is contrary to the history of the 20th century. I will skip the usual list of racial and social outrages perpetrated in the name of science and service of "absolute" truth. No doubt Colwell would reply that those were betrayals of the scientific process, and I would readily agree.

The problem is that when any group—technologists, humanists, or any groups ignorant of one or both decides that it has a lock on absolute

Computer

or even provisional truth, bad consequences follow.

The information overload issues currently reported with such breathless concern in the major news outlets and more than a few scientific circles have been encountered before. For example, the January 2003 issue of the *Journal* of the History of Ideas was entirely devoted to the topic of "Early Modern Information Overload." Realize that "early modern" in this context refers to the time period 1550-1750.

While the solutions developed at the time did not rely upon the transitor and its now distant cousins, the underlying principles were not all that different from modern information systems. The point being that if we avoid the obviously outlandish on either side, we can learn a great deal by studying both the hard and the difficult sciences.

Colwell starts from the position that "I'm right and you have been too lazy to learn why, so sit down and listen," which will not excite a lot of interest in his target audience. A better strategy would be to try to understand the other frame of reference before deciding that it is all that different from your own.

Will this strategy mean reading unfamiliar material and having to master new terminology? Yes, but it is also potentially rewarding in terms of new insights into your own discipline.

If the arts/science gap is going to be bridged, it will be by participating in both communities, not by missionaries bringing enlightenment to the savages. *Patrick Durusau Covington, Ga. patrick@durusau.net*

### Bob Colwell responds:

In my June column on "frames of reference," an idea that it is very difficult to communicate across different frames, I juxtaposed science and religion and science and the arts as pairs of representative differing frames. To find further evidence for the difficulties of communicating across frames, it isn't necessary to look any further than Patrick Durusau's letter.

Within the scientific frame of reference, most of its practitioners (including me) presume that an absolute truth exists. Scientists spend their lives looking for it; engineers spend their lives trying to stay close enough to it that their designs will work as intended. Durusau's computer works because these engineers succeeded.

The electrical charge on an electron is the same no matter who measures it, no matter where, and no matter what attitude or beliefs the measurer may have. Most of Durusau's letter seems aimed at the idea that science and the humanities are duals. In many ways they are, and thinking about those similarities may be enlightening to both camps.

But there is a basic way in which they differ, and Durusau has inadvertently highlighted it: Those in the sciences have a different standard for what they consider truth. When people in the humanities say that science has no monopoly on truth, I agree. But in an important sense, we're talking past each other. We don't mean the same thing; we're just using the same word.

Both sides ought to consider that each is using it within its own frame. That was precisely why I bridled at the mystic in the movie—she was using what she meant by "truth" as if it meant the same thing as when a scientist uses it, thus propagating an insidious logical error.

Durusau missed one other major point of the article: It was aimed precisely at *Computer*'s readership, and not at anyone from any other frame of reference. I therefore intentionally used the terms and context that are appropriate to that frame. Were I to have written a similar article for a humanities journal, substantial translation would have been required so as to reach that readership without giving offense. That was the point of the article.

### **CAMP A INSIGHT**

Regarding Bob Colwell's June column, I think Camp A is actually all right with Camp S. We need a different label than "art" for the other side.

I say this from my experience teaching a new course at the Maryland Institute College of Art titled "Foundations of a Scientific World View." It's a very selective school—these are top-notch kids with great artistic gifts and motivations, and they're no slouches when it comes to traditional academics either.

I also teach a course for graduate engineering students at Johns Hopkins titled "Logical Foundations of Computer Science." The art students have an unfair advantage, being full-time undergraduates versus the part-time graduate engineering students, but I'd have to say the art students are more inquisitive and open to a range of ideas compared to the engineering students. And the art students are very rigorous, too. The art faculty is also very inquisitive, open, and rigorous.

Maybe the opposite camp from Camp S is Camp B, for believers. Camp A is chock full of questioners. They seem to love a radical challenge to their preconceived notions. *Richard (DJ) L. Waddell Jr. Laurel, Md. richard.waddell@jhuapl.edu*

### Bob Colwell responds:

I can readily testify that most artists I've known have exhibited as much discipline and rigor as most engineers. But you know how stereotypes go: Artists are creative; engineers are drudges. I don't buy that one, either. Engineers are among the smartest people I've ever met (including all my science friends who are also very bright), and smart people are easily bored. I think people operating at the limits of human intellect and feasibility will always be creative, artist or engineer, and probably to the same extent. In my June column, I was primarily trying to find different frames of reference that the readers—who are mostly in the scientific camp—would readily understand, without inadvertently extending any stereotypes that should not be propagated. That's why I didn't address creativity, intelligence, inquisitiveness, and so on. I'm not trying to compare and contrast, per se; I'm only trying to show that the idea that differing frames cause differing interpretations of ideas and words is a useful meme.

My motivation is that within the next two to three decades, the probability is quite high that the world will face some fundamental challenges, of types that have never been seen before. Global warming, caused by the wholesale dumping of carbon into the atmosphere, could cause massive, unpredictable changes to the climate worldwide.

To what extent should we make sacrifices today on behalf of future generations, and based on what data and climate models? When the stakes are this high, we had better get this right.

Avoiding such catastrophes will require a reasonably deep understanding of many technical issues. That people not already embedded in the scientific realms must be bright, enthusiastic, and open to ideas is necessary but not sufficient.

The science folks who have studied this issue must find ways to get the information across to their Not Camp-S compatriots, or making communal intelligent decisions will be impossible. That is what I meant when I said the Camp-S folks must bridge the gap.

### **ARITHMETIC OPTIONS**

While my interest in reading "An Open Question to Developers of Numerical Software" by William Kahan and Dan Zuras (Standards, May 2005, pp. 91-94) kept up till the end, my perturbation grew from nothing to very great.

The authors state that the IEEE 754 Revision Committee's work is directed "into areas of expression evaluation, compiler optimizations, and other language issues that were considered outside the scope of the 1985 standard." Although the article opens with a general description, it is evident that the authors pose the open question because the committee members "wish to get rid of traps and of sNaNs if [they] can." The concluding remarks confirm that this is the primary concern, as does the e-mail address given for sending comments: snans@nonabelian.com.

The authors mention two excellent objectives: "Revisions of substance ... that would most help make modern floating-point programming easier and more reliable, efficient, and portable" and not to "make any change so sweeping it invalidates the operation of most of the world's computers."

What the authors seem to overlook is compatible extension. Defining standards for arithmetic on double (not double-length) numbers as well would best meet their worthy objectives.

There could be four modes of use: extended precision, combined operations on number pairs, operations on intervals, and operations on complex numbers—the last two being of most benefit in computation.

A method of interrogating whether the double arithmetics are available would make transition to the extended standard much easier.

Although the more popular programming languages do not as yet have types available for such extensions, the arithmetic could come into prompt and effective use in standard library code.

The availability of full support for interval arithmetic would benefit technical computation and promote wider use of the proven validated numerics techniques. The availability of full support for complex arithmetic would greatly improve both technical computation and graphical computation, which is of such commercial significance and magnitude that chipmakers might well be persuaded to adopt a new extended standard much earlier than if it merely benefited engineers.

I am not a numerical software developer, and many such developers would be better able to judge the benefits of this kind of extension. If I am wrong, so be it. But if I am right, and if the benefits are as great as I imagine, this is an opportunity for experts to offer the Revision Committee their opinions and their help. If the committee is to extend the standard in this way, they will need the best help they can get.

Neville Holmes University of Tasmania Neville.Holmes@utas.edu.au

### The authors respond:

Neville Holmes is quite right in stating that the primary goal of our article was to get feedback on the narrow issue of signaling NaNs.

The IEEE 754 Revision Committee has considered many of the extensions Neville mentions, along with others. However, doubled-double generally is an unreliable arithmetic to use for computation.

Suppose a C++ program using float and double variables and constants has been proved to work well, but greater accuracy is desired. One way to achieve that is to promote all double variables and constants to doubled-double (most likely called "long double"), promote all float variables and constants to double, appropriately shrink tolerances controlling iteration convergence, add terms to truncated series, and so on.

Would the promoted program work as well as the old, but twice as accurately? Not necessarily. The promoted program could suffer from mysterious rare malfunctions none of which could afflict the code if quadruple had been used instead of doubled-double.

This is why the committee has chosen to standardize the honest 128-bit quad format already in common use. At least one chip designer has announced full hardware support for quadruple at full speed.

The IEEE 754r committee has avoided attempting to specify complex arithmetic for three reasons.

First, C99 does a good job. It specifies an imaginary type and then defines the complex type as a formal (unevaluated) sum of a real and an imaginary. Doing so avoids several nasty anomalies in the complex type as Fortran and some packages used in C and C++ specify.

Second, as good as the C99 specification may be, it still suffers from some conundrums. For instance, multiplication that handles complex infinities well is too slow for matrix multiplication.

Correctly rounded complex multiply is probably too much to ask even from systems with a fused multiplyadd but not quadruple in hardware. Correctly rounded complex divide still costs too much.

Third, nothing IEEE 754r can say will change entrenched complex arithmetic practices, but attempts to change them might well jeopardize acceptance of the rest of IEEE 754r. Maybe some day.

We have looked into interval arithmetic and a standard set of transcendental functions. Our reluctant conclusion is that the state of the art is not yet up to standardizing these functions in a way that our posterity would surely find satisfactory.

Some things need to be standardized now:

- control of expression evaluation,

- alternate methods of exception

- handling, and

- aids to debugging.

Our work is not yet finished. The committee's deliberations are open to anyone who wants to participate (grouper.ieee.org/groups/754/), including those who are not members of the IEEE.

For details about these and other issues see www.cs.berkeley.edu/ ~wkahan.

William Kahan and Dan Zuras

# COMPUTATION AND COMMUNICATION

In "Socially Aware Computation and Communication" (Mar. 2005, pp. 33-40), Alex Pentland discusses some interesting cutting-edge ideas for building machines to understand human behaviors in terms of "quantifying social context in human communication."

In addition to being the underpinnings of mental partnerships, nonlinguistic signals such as body language, facial expression, and tone of voice are what make humans the most complicated animal. However, how well an expert system could understand and interpret such signals would depend on its capacity to make inferences or draw conclusions. It is not a question of how to build such an expert system, but rather whether the system will work.

In general, an expert system consists of two important components: a knowledge base and reasoning. This base consists of factual knowledge and heuristic knowledge.

Factual knowledge is a vast collection of widely shared and commonly used information. How people use this collection of knowledge depends on multiple factors such as their age, education, culture, gender, and so on. In addition, the same behavior could have a different meaning in a different situation or a different culture.

In some cases, knowledge is incomplete or uncertain. While it's possible to apply the concept of "fuzzy logic," assigning an associated confidence factor or weight, these scenarios might excite a human's imagination but probably not a machine's.

Heuristic knowledge is useful in testing the efficacy of an intelligent system because it requires making judgments, but this could cause plausible reasoning to be ineffective. For example, if people do a good job of pretending, how would forming a line of reasoning using either forward chaining or backward chaining of IF-THEN rules handle interpreting their behavior?

That is what makes simulating the human brain extremely difficult, and I believe no machine can ever replace it.

As a side note, if researchers could build a machine for making important decisions like finding a mate, getting a job, negotiating a salary, or finding a place in a social network, would it become a hindrance to human thinking?

Although we don't know when such a machine might become available, and it seems unlikely that it would be effective in dealing with the real-life situations, I fully support the spirit of this wonderful pursuit of the concept of building intelligent systems. *Hong-Lok Li Vancouver, BC lihl@ams.ubc.ca*

### EMBEDDED ENTERTAINMENT

Readers of my article on smart projectors published in *Computer*'s January 2005 issue ("Embedded Entertainment with Smart Projectors," pp. 48-55), might be interested in finding information about a related project. The authors of "Making One Object Look Like Another: Controlling Appearance Using a Projector-Camera System" (M.D. Grossberg et al., *Proc. IEEE Conf. Computer Vision and Pattern Recognition*, vol. 1, IEEE CS Press, 2004, pp. 452-459) describe a projector-camera system that addresses the problem of radiometric compensation on 3D surfaces with a different technical approach and application orientation.

Oliver Bimber Bauhaus-University Weimar bimber@uni-weimar.de

We welcome your letters. Send them to computer@computer.org.

# 28th International Conference on Software Engineering 20-28 May 2006

## http://www.icse-conferences.org/2006/

ICSE 2006 will be held in Shanghai, China, a main epicenter of the explosive growth of the software industry in China during these early years of the 21st century. ICSE 2006 will be a signal event in the recognition of this growth, and in the bringing of the Chinese software engineering community into the ICSE mainstream. The web site will detail traveling arrangements as well as the many ICSE activities to be held in Shanghai, a city that blends the dazzlingly ultramodern and the charmingly traditional. A visa is needed for travel—please visit the web site for more information and other conference details. Travel costs less than you think, so join us in Shanghai in May 2006 for

| costs less than you think, so join us in Shanghai in May 200 | 1 |

|--------------------------------------------------------------|---|

| an experience that will combine outstanding technical        |   |

| events with a visit to a city and country                    |   |

| that will be truly unforgettable!                            |   |

|                                                              |   |

| Major Submission Deadimes                                           |             |  |

|---------------------------------------------------------------------|-------------|--|

| Research Track                                                      | 9 Sep 2005  |  |

| Education Track                                                     | 1 Oct 2005  |  |

| Workshop and Tutorial Proposals                                     | 6 Oct 2005  |  |

| Experience, Far East Experience,<br>Research Demos, Emering Results | 30 Oct 2005 |  |

| Doctoral Symposium                                                  | 5 Dec 2005  |  |

Major Submission Doadlin

### **JULY 1973**

**ELECTROCARDIOGRAPHY** (p. 21). "The central issue is, of course, how we can provide more expeditious and efficient [electrocardiography] service. A computer can help us achieve this.

"We can quote from a publication entitled 'Computer Assisted Medical Practice: The AMA's Role' published by the AMA in 1971. 'It is reasonable to expect that government and industry will make broader commitments to develop further the applicability of the computer to medical practice. The ultimate responsibility for the effective utilization of computers, however, will lie within the medical community.' Correctly it is up to physicians to assure that efforts are successful. To do this they must begin to invite engineers into the clinical area. A case against computer electrocardiography can be made. One wonders who after even the shortest study would really want to make it."

**INTENSIVE CARE** (p. 29). "The application of technology and system engineering techniques to the delivery of health services has made possible the successful implementation of a computer-based system in the clinical care of patients during the crucial early hours following heart surgery."

"Routine, repetitive tasks which are well defined have been relegated to the system, enabling the nurses to devote more of their time to direct patient care. The computer automatically acquires the clinical measurements simultaneously from four patients each two minutes, displays and stores the current values, retrieves past data for review at bedside on command and periodically tabulates the data in hard copy form to be included in the patients' hospital records, relieving the nurses of nearly all measurement and charting chores."

**SHEET PRINTER** (p. 35). "Xerox Corporation has announced a new non-impact computer printing system that produces copy on  $8^{1/2} \times 11$ -inch, ordinary, unsensitized paper faster than a page a second, or up to 4,000 lines per minute."

"It is about twice as fast as standard impact-type computer printers now on the market ... and does away with a need for the large, unwieldy paper and pre-printed forms on which computer print-out has been produced in the past.

"A key advantage of the Xerox 1200 computer printing system is the elimination of the bursting and decollating operations—removing carbon paper and separating continuous-form sheet—associated with impact printers."

**DISPLAY TERMINAL** (p. 36). "A new CRT Data Display Terminal announced by Lear Siegler, Inc. has been described as a 'breakthrough' in the area of cost vs. performance. Exhibiting an impressive list of capabilities, the new terminal has been priced at under the \$1000 level in quantities and is listed at \$1500 in single units, roughly half the cost of conventional devices."

"Performance-wise, the ADM-1 has capabilities match-

ing and exceeding most conventional CRT terminals. The display format of the terminal is 960 characters (12 lines of 80 characters), using 64 alphanumeric US ASCII characters in a  $5 \times 7$  dot matrix. An optional screen is also available with 1920 characters consisting of 24 lines with 80 characters each."

**COMPUTER ANIMATION** (p. 40). "The computer has moved past science and business and into the creative arts with the announcement of 'SynthaVision', a process that makes multi-dimensional color films, completely by computer, without requiring the existence of an original 'except in the mind'—with realism comparable to photographs of an existing object.

"Representatives of the nation's leading advertisers and their agencies, television and film production companies, scientists, educators and urban planners attended the first in a two-day series of presentations ... They saw a 22minute demonstration film and heard Dr. Phillip S. Mittelman, who conceived the process, say that with SynthaVision, 'you can now produce on film a simulation of almost any form or object imaginable. It can grow, shrink, change shape and size—anything you wish it to do and no original is required, only your idea of what it should look like and what it should do.'"

**LIGHTING CONTROL** (p. 41). "At the birthplace of William Shakespeare, one of the largest computerized lighting control systems in modern theater has been installed in the Royal Shakespeare Theatre, Stratford-Upon-Avon, England."

"Each lighting state set up during rehearsal is recorded by the system. The data recorded are the voltage levels required to drive each dimmer circuit. The values are stored in the computer's memory for use during the actual performances.

"The computer is connected to a control console, output devices, and a casette recorder. The system scans the lighting controls, interprets the commands given to it, computes crossfade data for each control channel—updating when necessary—and initiates control commands to the theater lights."

**INTERNATIONAL BANKING** (p. 41). "S.W.I.F.T. (Society for Worldwide Interbank Financial Telecommunication) has been legally incorporated as a non-profit making society and the board of directors held its first meeting in Brussels.

"The S.W.I.F.T. network will carry financial transactions for a consortium of international banks. Out of a total of 256 banks which have participated in the design phases of the project 239 have now become members of S.W.I.F.T. They represent the major commercial and central banks in 13 countries in western Europe as well as in Canada and the United States."

"The S.W.I.F.T. network is planned to come into operation in 1976. It will be a store and forward switching network designed so that users with terminals of different speed and type can communicate with each other."

### **JULY 1989**

**SDI LETTER** (p. 5). "In short, SDI can only be called reliable by tampering with the very notion of reliability itself. Not all of the conferences, speeches, statistics, or appropriations in the world will change this fact. SDI has no intellectual credibility—it is the 'creation science' of the engineering world. Blandly reporting the double talk from the latest SDI conference is no service to the public. Who, except those bellying up to the federal feed trough, can think that SDI is worth \$30 billion in software development costs? As an engineer, I say, let's build projects that actually work. As a taxpayer, I say, SDI is an outrageous grab for the federal purse, bleeding money away from legitimate projects, both military and civilian. Let's stop the SDI boondoggle."

**DYNAMIC SCHEDULING** (p. 21). "Many features of the pioneering CDC 6600 have found their way into modern pipelined processors. One noteworthy exception is the reordering of instructions at runtime, or *dynamic instruction scheduling*.... Another innovative computer of considerable historical interest, the IBM 360/91, used dynamic scheduling methods even more extensively than the CDC 6600.

"As the RISC philosophy becomes accepted by the design community, the benefits of dynamic instruction scheduling are apparently being overlooked. Dynamic instruction scheduling can provide performance improvements simply not possible with static scheduling alone."

**DESIGN RECOVERY** (p. 36). "Software maintenance and harvesting reusable components from software both require that an analyst reconstruct the software's design. Unfortunately, source code does not contain much of the original design information, which must be reconstructed from only the barest of clues. Thus, additional information sources, both human and automated, are required. Further, because the scale of the software is often large (hundreds of thousands of lines of code or more), the analyst also needs some automated support for the understanding process.

"Design recovery recreates design abstractions from a combination of code, existing design documentation (if available), personal experience, and general knowledge about problem and application domains."

**ASSOCIATIVE MEMORY** (p. 51). "Researchers have understood the basic principles of storing and retrieving data by content rather than by address for about 30 years. Despite this relatively long incubation period, information has spread slowly from the academic arena, and the technology has not been available to produce a successful commercial product. As a result, many designers have not developed the skills to work with associative and content-addressable memories. However, VLSI technology has improved the feasibility of associative systems and overcome many implementation obstacles."

**MULTIPROCESSOR SYNCHRONIZATION** (p. 66). "The growth of multiprocessors is evidence of an increasing focus on achieving high program speeds through parallelism. One of the primary problems confronting designers of multiprocessors is to provide efficient synchronization methods. The concurrent execution of programs may be limited by the parallelism exhibited in the control mechanism and by the associated overhead. A family of effective synchronization of parallel programs. Although synchronization is a long-standing area of research, existing solutions must be readdressed in the context of specific constraints posed by general-purpose, multiple-instruction, multiple-data (MIMD) architectures."

**100,000th MEMBER** (p. 82). "Mark Funkenhauser, a 30year-old Canadian researcher and graduate student, has been honored as the 100,000th member of the IEEE Computer Society.

"Funkenhauser became the society's 100,000th member on December 5, 1988. To commemorate that milestone, the society presented him a plaque May 17 during its 11th International Conference on Software Engineering in Pittsburgh."

**OFFICE AUTOMATION** (p. 102). "IBM says that its Office-Vision family of office-automation software is its first major System Application Architecture software application. The new software family reportedly provides integrated office functions across the OS/2, MVS, VM, and OS/400 operating systems."

**APPLICATION DEVELOPMENT** (p. 104). "Oracle has added the CASE Generator to its computer-aided systems engineering family of application development tools. According to the company, CASE Generator automatically generates portable applications directly from design specifications.

"CASE Generator receives definitions about an application's database tables and program module definitions from CASE Dictionary and translates the information into functional applications using SQL Forms, the company's fourthgeneration development tool. The resulting applications reportedly enforce all constraints and validation criteria in CASE Dictionary. They support lists of valid values, help and hint text, and automatic synchronization of data from multiple database tables."

Editor: Neville Holmes; neville.holmes@utas.edu.au.

# Judging Science Fairs

### **Bob Colwell**

rbitrary subjectiveness drives me crazy. I'd never have made it as a figure skater, for example. Apart from the requisite skill at skating, which disqualifies me right away, you would have to restrain yourself from physically attacking the judges after a competition, no matter how illogical, biased, self-serving, or obtuse their collective decision seems to be. And some randomness is built into the situation: "Artistic merit" can never be objective.

Auditioning for a play or an orchestra is much the same. Professionals have told me that even when a trumpet player is auditioning "blind"—behind a screen—after only a few notes, the judges will already know who he is. Does this bias their decisions? Well, they're human; if you're auditioning, it would be wise to expect subjectivity. Hope that you never offended them.

### **ENCOUNTERING CRYBABIES**

I once asked an NBA referee what it was like to call a game with flamboyant figures such as Dennis Rodman on the court. Surely it would be easier and yield a fairer overall result if the ref didn't have to consider the actual personalities involved?

The referee agreed, and without referring to any particular player, said that some of them were much more insistent than others about referees calling fouls. "Crybaby" was the word he used, and he said that the truly great players were never in that category. He cited Michael Jordan as his favorite—

Computer

Engineering must work or it's of little value, even in a science fair.

someone who never demanded special treatment, even when he knew a call had been blown. (As an aside, the ref said, "Hey, the players make mistakes, and so do we.")

This ref said that the crybabies don't accomplish what they hope for because by calling attention to themselves, they actually increase their chances of getting caught. Since they weren't exactly ingratiating themselves with the refs, any calls that could legitimately go either way were in greater danger of going against them.

### **INCENDIARY TOPICS**

We're told to avoid discussing religion or politics with people we don't know well because the chance of inadvertently generating an emotional tirade is so high. There's another conversational topic with the same incendiary potential: tastes in music.

Apart from disco, which most people except John Travolta, Donna Summer, and two of the three Bee Gees hated, it's extremely difficult to have a mutually beneficial conversation about, say, rap music's contribution to human society. It's amazing to me that people care so much about this and to observe how subjective their judgments about music really are.

It's not just culture—education matters too. You can learn to appreciate some kinds of music by taking into account the composer's intent, the environment, and the overall context. But in the end, each of us reserves the right to pass judgment on whether a particular aural offering is good or not.

### **THE BEST**

A perennial favorite topic in a classical guitar e-mail list is the question of which guitar is The Best.

If you're new to this topic, you might think that question has at least some hope of being answered rationally. For example, we might try to sneak up on it in several ways. What kinds of guitar do the finest players in the world use (never mind the battle over who those players are)? Maybe they all use the same kind, and we could narrow our search to just those. Which guitars cost the most? Surely there should be a correlation between price and quality.

If you polled all the best luthiers (there's that "best" thing again), would there be a pattern to their answers? Have any guitar competitions been held to try to shed light on this question? What if we actually measured a sample set of high-end guitars with appropriate audio equipment?

There are hundreds, possibly thousands, of classical guitar makers in the world. There are arguably fewer than 100 in the elite category of players that includes John Williams, Julian Bream, David Russell, and Elliott Fisk. And yes, there is a pattern to the guitars they play—it's clearly not a random linear distribution. For example, there appears to be a preference for the new carbon-reinforced "tops," which are reputed to generate more volume, a good thing for filling concert halls when playing an instrument with an intrinsically small voice. But are those new instruments sacrificing all-important tone to achieve that volume? If they are, is that a necessary price to pay, or will luthiers learn to get both? Nobody knows. And what we do "know" is ... subjective.

### SCIENCE'S OBJECTIVE UNIVERSE

If there's just one thing that the scientific paradigm got right, it was to automate the process for filtering ideas and theories before their general acceptance.

It doesn't matter what you think of me, or I of you. If your idea explains reality better than mine, then the scientific establishment should prefer yours.

In reality, of course, humans do the judging, and in any given case, they might get it wrong. The NBA ref must struggle to be fair when an overpaid crybaby is trying to do his job for him; the music audition judge must resolutely shut out any context that might interfere when she realizes who is playing on the other side of the curtain. And when you're refereeing a paper, you must constantly watch for your own biases, especially for submissions from rival schools or rival researchers.

What differentiates the scientific process from these other subjective judgments is our implicit retesting. We may get it wrong once in accepting or rejecting a paper, but over time, other people will retest the ideas in other contexts. Ideas that make it through that gauntlet will have been honed, shaped, and refined in the process, and in general, any personal biases will be filtered out.

There are corner cases to this nice, ultimately objective world. One of them is judging science fair competitions.

### **HIT ME WITH YOUR BEST SHOT**

Real-world designs are analyzed and evaluated by rival engineers, industry

analysts, buyers, and in the case of microprocessors, more Web sites than you would ever expect. Usually, these evaluations are done on a relative basis: Which browser is better, Internet Explorer or Firefox? Which operating system is better, Windows or Linux?

The evaluators take measurements, render graphs, and draw conclusions. These reviews are brutal, and they often make the product designer feel as though his children are being gratuitously and maliciously attacked.

### Implicit retesting differentiates the scientific process from other subjective judgments.

The more intrepid evaluations will also try to measure a real-world product in absolute terms. Your new laptop may exhibit an 8-hour battery life, and the best of the competition only five hours, but if some particular application requires three days, then your product will still be judged as lacking—as indeed it should be.

As a designer, I may not always enjoy these analyses, especially if I think they're unfair or biased. But I agree that real-world products should be held to the highest attainable standards.

### **JUDGING STRATEGIES**

While the best projects at a worldclass science fair like ISEF can hold their own with published research from anywhere, it isn't reasonable to expect the best engineering projects to do the same. There are many reasons for this, but one of the most important is that science has a lower barrier to entry: Individuals working alone can still have a good idea in math or science and have enough wherewithal to convince others it has merit.

Engineering, in contrast, also starts with ideas, but it usually also requires building something. Brilliant students are as creative as experienced engineers in industry, but they lack the experience to know how best to apply it. They also seldom have access to an industrial design team's resources for realizing their idea, and they can't hope to compete with a competent design team in terms of design-hours, tools, and experience. Moreover, engineers usually work on projects that are expected to yield a lucrative outcome—there's money involved and therefore there's strong motivation.

How then can we fairly judge a science fair effort in engineering at the high school or college level? If you compare it against standard industrial practice, it will inevitably come up short. But if you only compare the projects against the other submissions, what feedback should you give the submitters about their work's merits and drawbacks?

I've judged many such events. There are a few things that are said at every closed-door judging session: "These are only high school (or college) submissions; you can't expect them to hold up to professional standards." Or "What were *you* doing in high school?" Or "Aren't you being way too hard on these poor kids?"

All things considered, I believe the best strategy is to judge submissions both ways: 1) relative to each other, and 2) absolutely, against the highest standards the judges can conceive.

### Why judge relatively?

The point of a high school science fair or college-level science competition isn't to generate new knowledge or fundamental contributions to the engineering experience base, although that does occasionally occur. The point is for the students to have fun with science and engineering, further their knowledge and ability, and remain engaged with the technical process.

Kindergarten through eighth-grade science fairs are noncompetitive. I have mixed feelings about that. Especially for the youngest exhibitors, it would make little sense to try to identify "the best" because it would be counterproductive in terms of making kids like science (it's not much fun to lose). Also, to be frank, even the best of these tend to be not very good, so overly rewarding them would (within a few years) turn into a mixed message for the budding scientist.

The challenge is to give the students who are really trying enough useful feedback so that they learn and grow, without discouraging them about how far they have to go.

High school and college exhibitors want to know how they fared versus their peers. They want to know, "Am I any good at this science/engineering thing? Can I do it?"

I try to draw these students out on why they picked the topic, the ways they considered resolving it, and why they made their choice.

It's their reasoning ability, their ability to abstract out the essential elements of the puzzle and exclude whatever can be safely excluded, that I'm looking for. When I find that thread through their thinking, I highlight it and suggest that they've demonstrated that they possess the one trait no scientist or engineer can do without: the ability to make reasoned abstractions.

Searching for the best submissions helps to illuminate this process to all participants. There are degrees of thoroughness, shades of gray in how diligently students can strive to eliminate uncertainties from the work, a wide range of how much background research they can find to buttress their conclusions or help justify the study.

Only experience can inform the student's intuitions about how much is enough, and the science fair process is one such experience. Judging student projects against one another helps each student see where the judges believe those lines should be drawn.

### Why judge absolutely?

At the dawn of the nuclear era, the military was enthralled with the idea of atomic submarines that could stay submerged for a very long time, something the battery- and diesel-powered subs of World War II couldn't do. They asked if the same trick could be applied to aircraft: Was it possible to keep a bomber in the air for several weeks at a time, powered by nuclear fission?

Fortunately, the answer turned out to be no (would you want nuclear reactors flying over your head?). The materials required to shield a nuclear reactor for nearby humans turn out to be very heavy. Not a problem for submarines and ships, but an insurmountable issue for aircraft.

Both relative and absolute judging are essential to achieving the right balance of fun and education in science fairs.

Imagine a science competition in which the best three engineering submissions turned out (by coincidence) to be different designs for atomic aircraft. After intense scrutiny of these projects, a consensus ranking by the judges might well emerge. But the judges might also conclude that none of the three submissions was, in fact, workable.

Rough edges on a prototype are understandable and to be expected engineering submissions that could encounter economic or fabrication challenges could be wonderful despite obvious flaws in the prototype being displayed. Professional engineers everywhere will recognize that truth; they live it every day.

Economic issues can be overcome with high sales volume (witness LCD displays); better tools or specialized manufacturing techniques (blue LEDs, for example) can overcome fabrication challenges. But if the project's fundamental premise is flawed, it is doomed in a way that no pretty display poster can possibly fix.

Judges have a responsibility to make this clear to the project submitters. It's not enough to be the best of a bad lot. Engineering must work or it's of little value, even in a science fair.

I have seen several instances in which perpetual energy machines made it to ISEF. In each case, the combination of bright, engaged students and the clear evidence that they aren't getting appropriate guidance from their teachers (and the judges they somehow got by at lower levels of competition) was profoundly depressing to me.

Should every project that even appears to rely on—or produce—perpetual motion be automatically excluded from ISEF? No, I wouldn't go that far. As a matter of practicality, the US Patent Office is within its rights to auto-exclude such things from consideration for patent protection. But science as a whole must not.

However, what must be made clear to such students is the fundamental, inescapable truth that "Big Claims Need Big Proofs." If you're going to claim perpetual motion, or cold fusion for that matter, you need compelling evidence. Your work is going to undergo extraordinary scrutiny, and thorough preparation for such an ordeal is much better done beforehand and in private, rather than after you've staked the claim.

### **THE BURDEN OF PROOF**

Turning science on its head is among the most revered accomplishments to which students can aspire—Albert Einstein is the patron saint of such efforts. But the burden of proof for such things is extremely high.

More commonly, in the best tradition of engineering, students will find something in their own environment that they believe they can improve. The family car, for example: It breaks down, it gets into accidents, its driver may be impaired or lost, and the interior sometimes gets hot enough to kill pets or children.

The students imagine ways of having the vehicle sense its surroundings, automatically communicate with other vehicles, and autonomously contact the nearest hospital upon detecting that the airbags have deployed. They propose "black boxes" to collect information about automobile collisions. They work out bandwidths, power levels, cost, packaging, and programming. The best students even prototype the system and try it out in the lab. When it functions as expected, they declare victory and make their poster for the competition.

A real-world engineering team would consider things far beyond the obvious technical basics. The automotive environment is a very hostile place for electronics—everything must work correctly, every time, in Fairbanks, Alaska, in late January and also in Death Valley, California, in August. Those temperature extremes are much wider than normal commercial-grade electronics parts are guaranteed to handle.

Because they're mobile, cars can also drive close to antennas pumping out kilowatts of radio-frequency power. Keeping electronics working correctly in the face of this onslaught requires careful attention to grounding, shielding, and signaling.

More subtle, for most students, are the not-quite-science issues that surround a real-world design. How do you reliably detect that a driver is getting drowsy? Is there a single reliable way to detect sleepiness? Head position? Drooping eyelids? The car wandering across lane markers? Having disco come on the radio and not quickly changing the station?

What should the system do if it determines that the driver has become drowsy—find a heavy-metal station and turn up the radio? If the system malfunctions and begins to annoy the driver, is it possible to temporarily turn it off?

How would you know that a scheme for having an automobile communicate with a hospital works? Will it routinely ping nearby hospitals, or will it just do a power-up self-test when you start the engine? Is the Internet reliable enough to incorporate into such a scheme? Perhaps most difficult for students are the legal issues, which can differ radically from one country to the next. How do you design fail-safe automotive products? You already know that a black box recorder for a car must be designed to survive a high-G crash and ensuing fire. But how will you keep it from being hacked to make it seem as though the other driver was at fault? Who owns the information in that black box, in a legal sense? How trustworthy would the data be considered in a court of law?

I wouldn't expect students to have convincing answers to these questions, but if they're going to design for the automotive arena, they must at least consider them.

nly by illuminating the gap between a given project and what the real world would require will students be able to recognize the value of their contribution and the size of the learning curve they have yet to climb.

The best students already operate at the highest levels of intellect; we should honor them by treating them as respected colleagues and never be patronizing or condescending about their efforts.

The optimum balance between relative and absolute judging will differ between the best students and the rest, but both kinds of judging are essential to achieving the right balance of fun and education.

**Bob Colwell** was Intel's chief IA32 architect through the Pentium II, III, and 4 microprocessors. He is now an independent consultant. Contact him at bob.colwell@comcast.net.

# **Eclipse Becomes the Dominant Java IDE**

### **David Geer**

ince Sun Microsystems introduced Java in 1995, proponents have sought ways to boost the technology's fortunes. One approach has been to create an integrated development environment that would make working with Java easier.

Supporters hoped an IDE would make Java more competitive with Microsoft's popular Visual Studio .NET, which provides an environment for integrated, easy-to-use software tools that appeal to the many businessapplication developers who aren't hard-core programmers.

This has set off a battle among several Java IDEs, including Borland's JBuilder, Microsoft's Visual J#, Oracle's JDeveloper, and Sun's NetBeans.

One contender has been Eclipse, which IBM developed and turned over in 2001 to the nonprofit Eclipse Foundation (www.eclipse.org) to manage as an open-source platform.

In addition to providing an IDE, Eclipse automates numerous functions that developers would otherwise hand code, said Alan Zeichick, editor in chief of *SD Times*, a newspaper for software-development managers.

Eclipse has garnered so much support that many industry observers say it is now the key Java-tools player. Today, the Eclipse Foundation has 98 member companies, including most of the largest software vendors. The technology even

Computer

has its own annual conference, EclipseCon, which sold out this year.

"Eclipse has truly won," said Zeichick. It is inexpensive to use and makes it much easier to integrate their tools with one another, he added.

### **ECLIPSE HISTORY**

Object Technology International developed the Java-based technology behind Eclipse before IBM bought the company in 1996. IBM began working on Eclipse internally in 1998 to integrate its many development programs.

IBM designed the Eclipse platform in accordance with standards set by the Object Management Group (www. omg.org), which produces and maintains specifications for interoperable enterprise applications.

Although the Eclipse Foundation now manages the platform, nonmembers can also build applications using the technology.

### **HOW ECLIPSE WORKS**

Multivendor IDEs are a key factor in software design. They let a project's developers select their preferred tools from different vendors without worrying about making them work together or learning multiple interfaces and programming environments.

Like other IDEs, Eclipse is a programming environment packaged as an application. It consists of a code editor, compiler, debugger, GUI builder, and other tools.

For example, the Eclipse Foundation has included refactoring tools, which conduct a series of small transformations to restructure an existing body of code—for example, to make it smaller and less buggy—without changing its external behavior, noted Ian Skerrett, the organization's director of marketing.

The foundation has also added intelligence to the text editor, which is used for hand coding, Skerrett added.

Eclipse offers a set of APIs that connect tools into one unit, the Generic Workbench, that works as a single development environment with one set of behaviors and interfaces.

Eclipse uses the Standard Widget Toolkit to provide programs' interfaces. The IBM-created SWT is a class library for creating GUIs in Java. It lets developers build portable applications that directly access the user-interface facilities of the operating systems on which they are implemented. The Java programs thus look like native desktop applications.

Proponents say that because the SWT works with the operating system, it will perform better than techniques that bring their own UI features and thereby create user interfaces that look the same regardless of the host OS.

Meanwhile, Eclipse automates functions, such as the creation of buttons and dialog boxes, that developers might otherwise have to hand code.

Eclipse is built with Java and thus runs on multiple platforms. However, it will also help build applications in other languages such as C, C++, Cobol, and HTML.

### **REASONS FOR ECLIPSE'S SUCCESS**

"Among the top Java IDEs, Eclipse is the only one gaining market share in Europe, the Middle East, Africa, Asia-Pacific, and North America," said analyst Albion Butters with Evans Data, a market research firm.

"The power of Eclipse is the common platform that you can integrate different tools into," said the Eclipse Foundation's Skerrett.

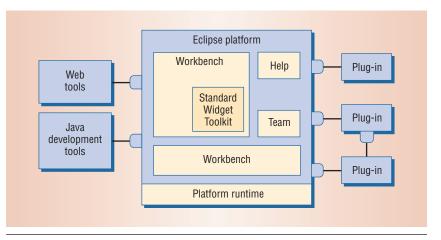

Eclipse was created as a platform for plug-in tools that extend the IDE's capabilities so that it can work with numerous programming languages and applications, as Figure 1 shows. Anyone can write plug-ins for Eclipse and have them work directly with any other plug-ins for the platform. Some other IDEs limit plug-in creation to company partners.

There is thus a "huge number" of interoperable third-party plug-ins, which has made Eclipse very popular, said John Andrews, Evans Data's chief operating officer.

IBM's release of Eclipse to the Eclipse Foundation made the technology independent of any company, which fueled its broader adoption by businesses that don't want to be tied to a specific vendor, noted Rob Cheng, Borland's director of product marketing. "The more independent Eclipse is, the more comfortable companies and developers feel using it," he explained.

For example, Oracle is working to ensure that any developer using Eclipse can build applications for the vendor's application server and database, explained Ted Farrell, chief architect in the company's Application Development Tools Division.

### Lower costs

The entire Eclipse development platform is free. Proprietary IDE systems such as JBuilder, JDeveloper, and JetBrains' IntelliJ IDEA, on the other hand, can cost up to \$3,500 each.

Users seeking to add plug-ins that aren't part of Eclipse can get some tools for free and pay for others. Either way, it can be less expensive than buying an entire proprietary development platform.

Figure 1. Eclipse was created as a platform for plug-in tools that extend its capabilities so that it can work with numerous programming languages and applications. The tools plugged into the platform operate on regular files in the user's workspace. Eclipse can place a project in the workspace under version and configuration management with an associated team repository. On startup, the platform runtime discovers the set of available plug-ins, reads their manifest files, and builds an in-memory plug-in registry. The workbench provides Eclipse's user-interface personality and includes the SWT general-purpose UI toolkit.

Eclipse's popularity has led many tool developers to make their products compatible with it. This competition has reduced the price of the plug-ins that aren't free, according to Evans Data's Andrews.

## Fast-moving innovation and development

Because Eclipse is open source, Borland's Cheng said, developers have ready access to the source code and can modify it and innovate quickly to meet users' needs.

And, Cheng added, companies like the technology's open development process. "It is a very transparent process. Most of the communications, milestones and plans are public, and the builds are available for public download. Interim builds come out every couple weeks or every month so that people can try it out and give feedback quickly. There is a lot of community involvement," he said.

### **Elegant architecture**

According to Cheng, Eclipse is a small, modular IDE with an elegant architecture that starts from a basic but

powerful foundation. "There is a layer that lets you integrate applications without worrying about drawing dialog boxes, buttons, and widgets or property pages and project trees," he explained.

Thus, he elaborated, developers can hand code the new elements they need or want and disregard the elements that stay the same from program to program, such as dialog boxes.

### **NOT A TOTAL ECLIPSE**

Although it appears to be the Java IDE of choice, Eclipse still faces competition from alternatives such as JBuilder, Visual J#, JDeveloper, and NetBeans.

"Eclipse is certainly a very popular IDE and very successful," said Tim Cramer, software engineering director for Sun's NetBeans. "However, Net-Beans is seeing a resurgence with the developer community. Eclipse has been great competition, and because of this, we're all going to improve."

"With NetBeans 4.1," he added, "we now have a number of features that add value above and beyond what Eclipse might have: visual development of

# REACH Higher

Advancing in the IEEE Computer Society can elevate your standing in the profession.

Application to Seniorgrade membership recognizes

ten years or more of professional expertise

Nomination to Fellowgrade membership recognizes

exemplary accomplishments in computer engineering

GIVE YOUR CAREER A BOOST

www.computer.org/ join/grades.htm

### Industry Trends

J2ME (Java 2 Platform, Micro Edition) applications, debugging on a live cell phone, and an advanced profiler."

Thus, he said, "Our active users have gone up dramatically according to our internal measures, and we're also seeing a surge in traffic to our Web site."

### Concerns

According to Cramer, because Eclipse and the SWT are not going through Sun's Java Community Process for introducing new features, they don't create applications with true Java functionality.

In addition, he explained, developers must port the SWT to all platforms on which Eclipse runs, which can be complex, time consuming, and expensive. NetBeans, on the other hand, runs natively anywhere there's a 1.4 or later version of Java, he noted.

NetBeans originally used the Abstract Window Toolkit, an API for Java-application GUI development. Sun discovered performance and extensibility limitations with AWT and thus developed Swing, explained Cramer.

AWT uses the operating system's graphics code for GUIs while Swing brings its own, creating GUIs that look the same on any OS. In addition, Cramer said, Swing has about 500 classes of GUI-related objects and thus offers richer graphics and more components than AWT, which has only about 50 classes.

Because AWT and Swing are part of the Java specification, proponents say, they offer better Java functionality.

### **Oracle's compromise**

Concerned that Eclipse and NetBeans might create incompatible technologies that would split Java and make it less attractive to developers, Oracle has offered a compromise designed to enable compatibility.

The company has submitted Java Specification Request 198, "A Standard Extension API for Integrated Development Environments," to Sun's JCP. Rather than introduce yet another IDE, JSR 198 would provide a standard API that would work with all Java IDEs that support it.

The Eclipse Foundation has submitted for review Eclipse 3.1 Release Candidate 1, which features an updated SWT that offers more capabilities and interoperability with a greater number of browsers. The new version would also be faster, include more wizards, and enable automatic coding of additional features.

In addition, the foundation is expanding its activities. For example, the group's Web Tools Platform Project plans to begin releasing tools this summer. The organization has also developed business intelligence and reporting tools for generating reports from Java servers and is working on a richclient platform for developing robust desktop and workstation applications.