2009

ш

00

$\geq$

NOVE

Next Page

Innovative Technology for Computer Professionals

# Extreme-Scale Computing

MANAGING INTERNS, p. 93 WEB 2.0 INNOVATION, p. 96 COMPUTING ACCREDITATION, p. 102

http://www.computer.org

Celebrating 125 Years of Engineering the Future

Search Issue

Next Page

Contents

## ANNOUNCING A NEW STUDENT MEMBER PACKAGE FOR 2010! Join IEEE and the IEEE Computer Society and enjoy FREE access to the Computer Society Digital Library for only \$40

Now is the best time to become part of the world's leading technical community and benefit from numerous networking and real-world learning opportunities. And, student members have access to the Computer Society Digital Library (CSDL).

Whether you are looking for the latest research on today's hottest topic or quick answers to a problem, CSDL has the information you need. In addition to over 3,500 conference publications, CSDL includes

- Access to *Computer* magazine—featuring cutting-edge research and articles written by leading experts in the field

- All 27 Computer Society peer-reviewed periodicals covering the spectrum of computing and information technology—with access to the complete archives

Student members also receive

- Access to development software from Microsoft, including Visual Studio Team System, Vista Business Edition, and Expression Web Designer

- Access to 600 selections from Safari<sup>®</sup> Books Online, featuring technical and business titles from leading publishers such as O'Reilly Media, Addison Wesley, and Cisco Press

- Access to 3,000 courses powered by Element  $K^{\scriptscriptstyle (\! 8\!)}$  and available in numerous languages

- Valuable networking opportunities through membership in your local chapter

There has never been a better time to join both IEEE and the IEEE Computer Society.

Become a student member today for just \$40 by visiting www.computer.org/stuoffer

Editor in Chief Carl K. Chang Iowa State University

chang@cs.iastate.edu Associate Editor in Chief

Sumi Helal University of Florida <u>helal@cise.ufl.edu</u>

**Area Editors**

**Computer Architectures**

#### Associate Editor in Chief, Research Features Kathleen Swigger University of North Texas

Associate Editor in Chief, Special Issues Bill N. Schilit Google schilit@computer.org

kathy@cs.unt.edu

**Column Editors**

**Embedded** Computing

**IT Systems Perspectives**

George Washington University

Richard G. Mathieu

James Madison University

**Invisible Computing**

The Known World

**Education**

**Tom Conte**

Georgia Tech

Virginia Tech

**Bill N. Schilit**

David A. Grier

**The Profession**

**Neville Holmes**

Jeffrey M. Voas

Mike Hinchey Lero—the Irish Software

Security

SAIC

University of Tasmania

**Software Technologies**

**Engineering Research Centre**

Web Technologies

San Jose State University

Simon S.Y. Shim

Google

Green IT Kirk W. Cameron

Ann E.K. Sobel

Miami University

#### Computing Practices Rohit Kapur

rohit.kapur@synopsys.com

Perspectives

Bob Colwell

bob.colwell@comcast.net

Web Editor Ron Vetter vetterr@uncw.edu

#### Advisory Panel

**Thomas** Cain University of Pittsburgh Doris L. Carver Louisiana State University **Ralph Cavin** Semiconductor Research Corp. Dan Cooke Texas Tech University **Ron Hoelzeman** University of Pittsburgh Naren Ramakrishnan Virginia Tech **Ron Vetter** University of North Carolina at Wilmington Alf Weaver University of Virginia

#### **CS Publications Board**

Sorel Reisman (chair), Alain April, Angela R. Burgess, Frank E. Ferrante, David A. Grier, Audrey Kremer, Phillip A. Laplante, Paolo Montuschi, Jon Rokne, R. Sampath, Steve Seidman, Linda I. Shafer, Roy Sterritt, Steven L. Tanimoto

#### CS Magazine

Operations Committee David A. Grier (chair), David Albonesi, Isabel Beichl, Arnold (Jay) Bragg, Carl Chang, Kwang-Ting (Tim) Cheng, Fred Douglis, Hakan Erdogmus, Carl Landwehr, Dejan Milojicic, Sethuraman (Panch) Panchanathan, Crystal R. Shif, Maureen Stone, Fei-Yue Wang, Roy Want, Jeff Yost

2009 IEEE Computer

Susan K. (Kathy) Land, CSDP

**Society President**

president@computer.org

Steven K. Reinhardt AMD **Databases and Information** Retrieval **Erich Neuhold** University of Vienna **Distributed Systems** Jean Bacon University of Cambridge **Graphics and Multimedia Oliver Bimber** Baluhanes Keipeesittyn Weiningr Linz **High-Performance** Computing Vladimir Getov University of Westminster Information and **Data Management** Naren Ramakrishnan Virginia Tech Multimedia Savitha Srinivasan IBM Almaden Research Center Networking Sumi Helal University of Florida Software Dan Cooke Texas Tech University **Robert B. France** Colorado State University

## Contributing Editors

Lee Garber

**Bob Ward**

Scott Hamilton Senior Acquisitions Editor shamilton@computer.org Judith Prow Managing Editor jprow@computer.org Chris Nelson Senior Editor James Sanders Senior Editor

**Editorial Staff**

Design and Production Larry Bauer Design Olga D'Astoli Cover Design Jennie Zhu

#### Administrative Staff Products and Services Director Evan Butterfield Senior Editorial Services Manager Crystal R. Shif Magazine Editorial

Manager Jennifer Stout Senior Business Development Manager Sandy Brown Senior Advertising Coordinator Marian Anderson

Circulation: Computer (ISSN 0018-9162) is published monthly by the IEEE Computer Society. IEEE Headquarters, Three Park Avenue, 17th Floor, New York, NY 10016-5997; IEEE Computer Society Publications Office, 10662 Los Vaqueros Circle, PO Box 3014, Los Alamitos, CA 90720-1314; voice +1 714 821 8380; fax +1 714 821 4010; IEEE Computer Society Headquarters, 2001 L Street NW, Suite 700, Washington, DC 20036. IEEE Computer Society membership includes \$19 for a subscription to Computer magazine. Nonmember subscription rate available upon request. Single-copy prices: members \$20.00; nonmembers \$99.00.

Postmaster: Send undelivered copies and address changes to *Computer*, IEEE Membership Processing Dept., 445 Hoes Lane, Piscataway, NJ 08855. Periodicals Postage Paid at New York, New York, and at additional mailing offices. Canadian GST #125634188. Canada Post Corporation (Canadian distribution) publications mail agreement number 40013885. Return undeliverable Canadian addresses to PO Box 122, Niagara Falls, ON L2E 6S8 Canada. Printed in USA.

Editorial: Unless otherwise stated, bylined articles, as well as product and service descriptions, reflect the author's or firm's opinion. Inclusion in Computer does not necessarily constitute endorsement by the IEEE or the Computer Society. All submissions are subject to editing for style, clarity, and space.

**NOVEMBER 2009**

1

ഗ

~

ш

Z

Next Page

Innovative Technology for Computer Professionals

http://computer.org/computer

## ABOUT THIS ISSUE

E xtreme-scale computing relates directly to the hardware, software, and applications enabling simulations in the petascale performance range and beyond. As the articles selected for inclusion in this special issue demonstrate, in addition to enabling science through simulations at unprecedented size and fidelity, extreme-scale computing serves as an incubator of scientific and technological ideas for the computing area. An additional article explores the advantages of a commitment-based service-oriented architecture.

#### **COVER FEATURES**

#### 24 Extreme-Scale Computing— Where 'Just More of the Same' Does Not Work

#### **Adolfy Hoisie and Vladimir Getov**

In addition to enabling science through simulations at unprecedented size and fidelity, extreme-scale computing serves as an incubator of scientific and technological ideas for the computing area in general.

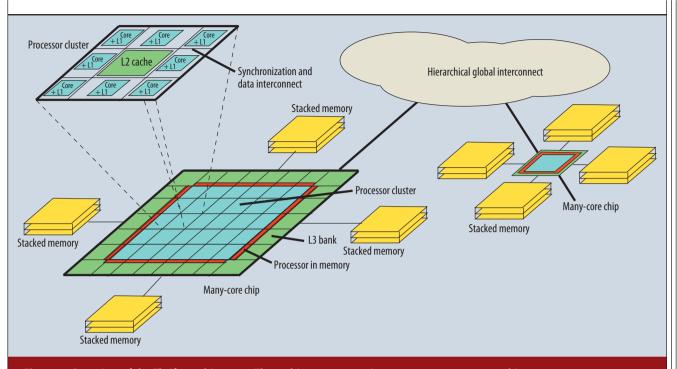

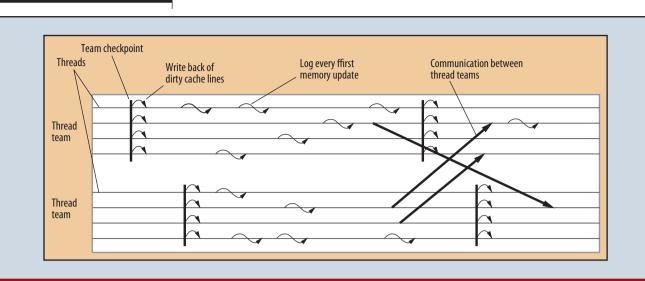

#### 28 Architectures for Extreme-Scale Computing Josep Torrellas

Extreme-scale computers promise orders-ofmagnitude improvement in performance over current high-end machines for the same machine power consumption and physical footprint. They also bring some important architectural challenges.

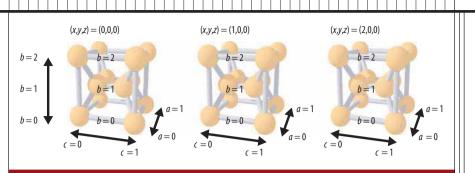

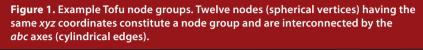

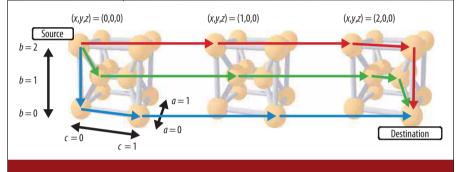

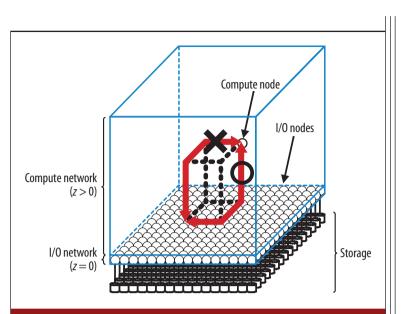

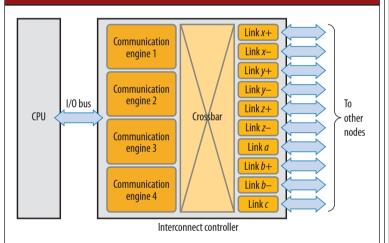

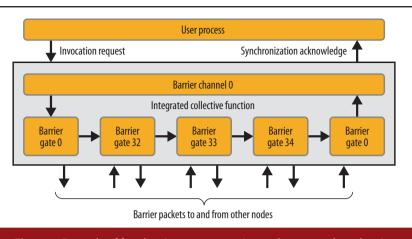

#### 36 Tofu: A 6D Mesh/Torus Interconnect for Exascale Computers

Yuichiro Ajima, Shinji Sumimoto, and Toshiyuki Shimizu

A new architecture with a six-dimensional mesh/ torus topology achieves highly scalable and faulttolerant interconnection networks for large-scale supercomputers that can exceed 10 petaflops.

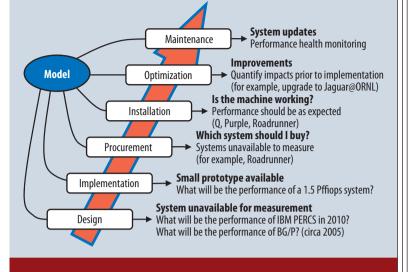

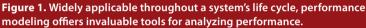

#### 42 Using Performance Modeling to Design Large-Scale Systems

Kevin J. Barker, Kei Davis, Adolfy Hoisie, Darren J. Kerbyson, Michael Lang, Scott Pakin, and José Carlos Sancho

A methodology for accurately modeling large applications explores the performance of ultrascale systems at different stages in their life cycle, from early design through production use.

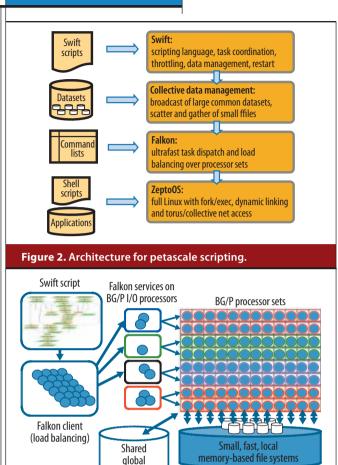

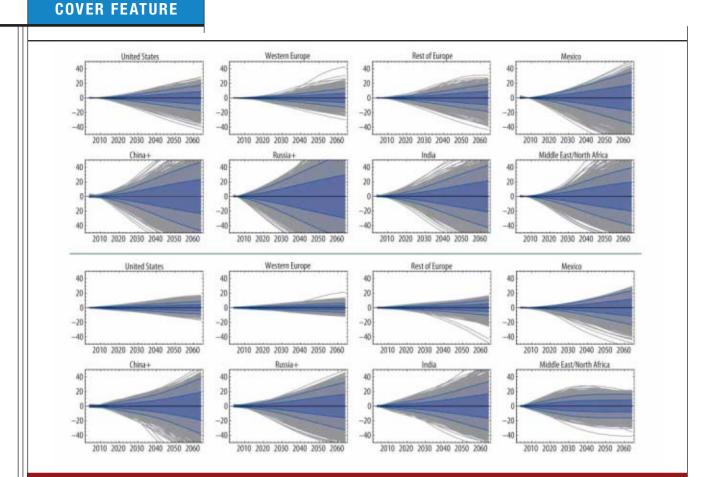

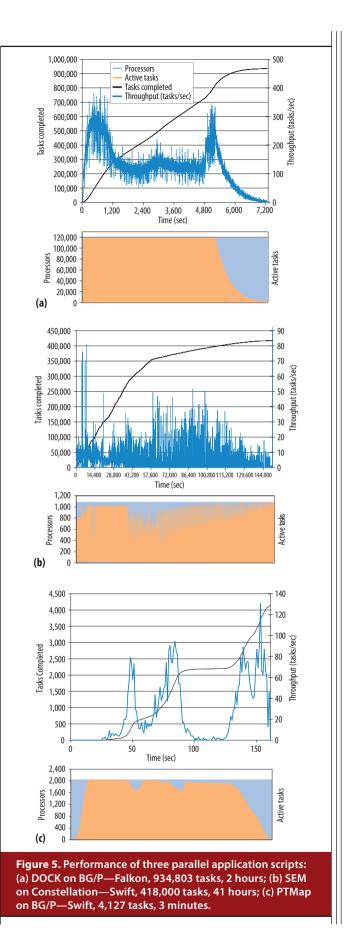

#### 50 Parallel Scripting for Applications at the Petascale and Beyond

Michael Wilde, Ian Foster, Kamil Iskra, Pete Beckman, Zhao Zhang, Allan Espinosa, Mihael Hategan, Ben Clifford, and Ioan Raicu

Scripting accelerates and simplifies the composition of existing codes to form more powerful applications. Parallel scripting extends this technique to allow for the rapid development of highly parallel applications that can run efficiently on platforms ranging from multicore workstations to petascale supercomputers.

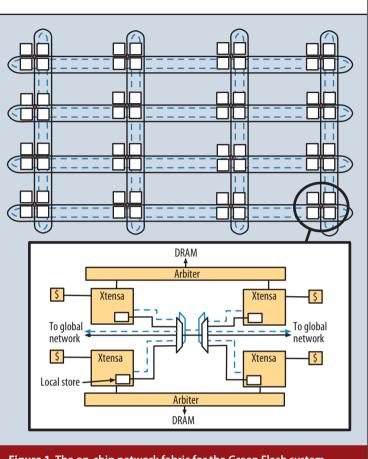

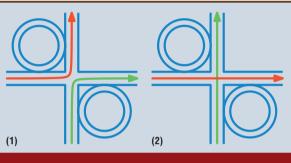

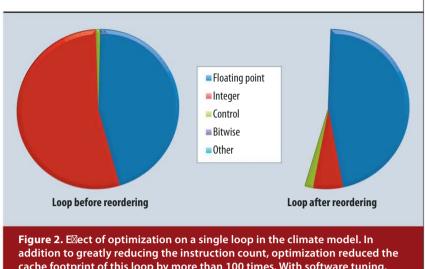

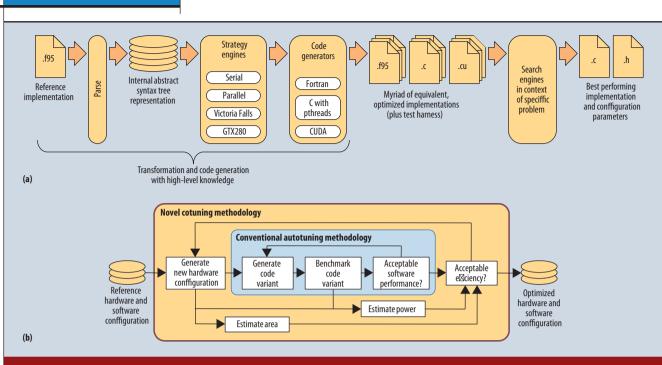

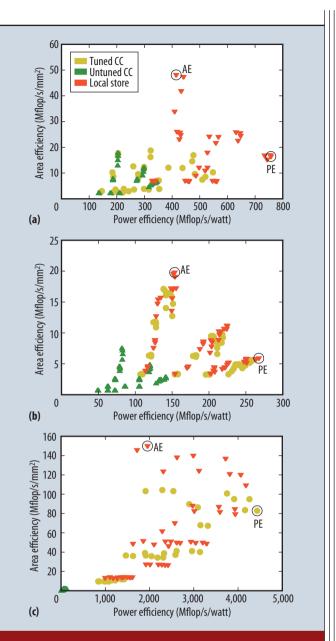

#### 62 Energy-Efficient Computing for Extreme-Scale Science

David Donofrio, Leonid Oliker, John Shalf, Michael F. Wehner, Chris Rowen, Jens Krueger, Shoaib Kamil, and Marghoob Mohiyuddin

A many-core processor design for highperformance systems draws from embedded computing's low-power architectures and design processes, providing a radical alternative to cluster solutions.

#### **RESEARCH FEATURE**

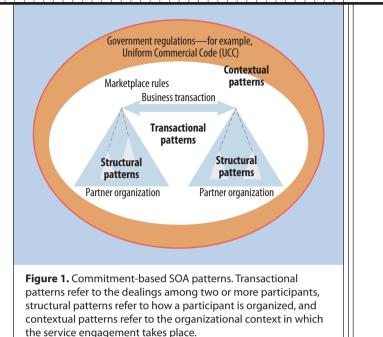

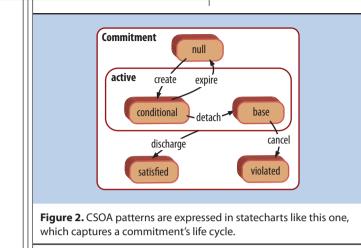

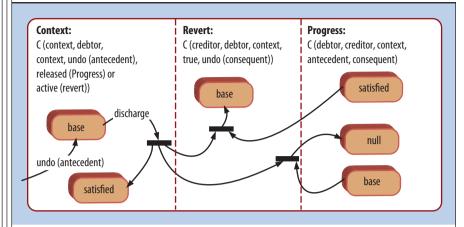

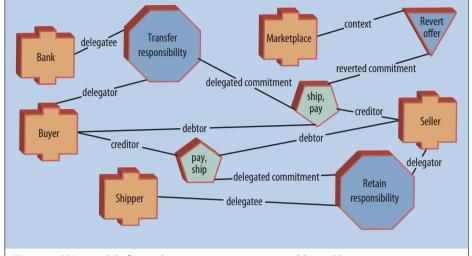

#### 72 Commitment-Based Service-Oriented Architecture

Munindar P. Singh, Amit K. Chopra, and Nirmit Desai

Existing service-oriented architectures are formulated in terms of low-level abstractions far removed from business services. In a new SOA, the components are business services and the connectors are patterns, modeled as commitments, that support key elements of service engagements.

For more information on computing topics, visit the Computer Society Digital Library at www.computer.org/csdl.

Computer

**q**Mags

IEEE Computer Society: http://computer.org Computer: http://computer.org/computer computer@computer.org IEEE Computer Society Publications Office: +1 714 821 8380 Cover image © Andreus I Dreamstime.com

8 The Known World Bad Alignment David Alan Grier

12 32 & 16 Years Ago Computer, November 1977 and 1993 Neville Holmes

#### NEWS

#### 15 Technology News Anonymization Technology Takes a High Profile Neal Leavitt

20 News Briefs Linda Dailey Paulson

#### MEMBERSHIP NEWS

87 IEEE Computer Society Connection

**90** Call and Calendar

#### COLUMNS

93 Industry Perspective Managing Interns Shel Finkelstein

96 Web Technologies Innovation for the Web 2.0 Era Miguel Carrero

#### Flagship Publication of the IEEE Computer Society

Mass

CMass

#### November 2009, Volume 42, Number 11

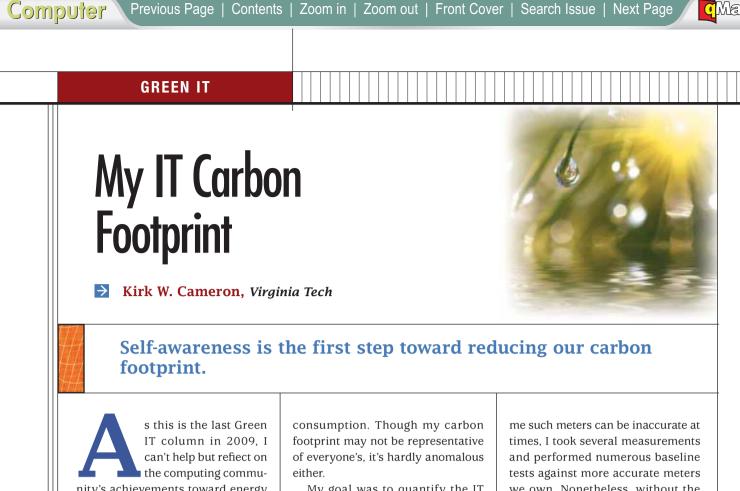

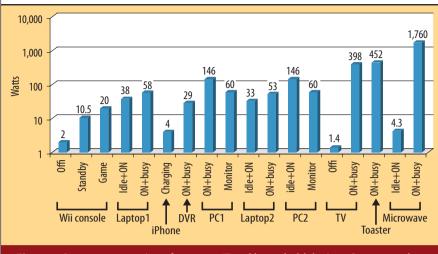

| <b>99</b> | Green IT               |

|-----------|------------------------|

|           | My IT Carbon Footprint |

|           | Kirk W. Cameron        |

|           |                        |

#### 102 IT Systems Perspectives Global Trends in Computing Accreditation Harry L. Reif and Richard G. Mathieu

#### 108 The Profession Truth and Breadth, Clarity and Depth in Algebra Neville Holmes

#### DEPARTMENTS

- **4** Elsewhere in the CS

- 6 Letters

- 61 Computer Society Information

- **80** Career Opportunities

- 86 Advertiser/Product Index

- 92 Bookshelf

Reuse Rights and Reprint Permissions: Educational or personal use of this material is permitted without fee, provided such use: 1) is not made for profit; 2) includes this notice and a full citation to the original work on the first page of the copy; and 3) does not imply IEEE endorsement of any third-party products or services. Authors and their companies are permitted to post their IEEE-copyrighted material on their own Web servers without permission, provided that the IEEE copyright notice and a full citation to the original work appear on the first screen of the posted copy.

Permission to reprint/republish this material for commercial, advertising, or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to the IEEE Intellectual Property Rights Office, 445 Hoes Lane, Piscataway, NJ 08854-4141 or pubs-permissions@ieee.org. Copyright © 2009 IEEE. All rights reserved.

Abstracting and Library Use: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy for private use of patrons, provided the per-copy fee indicated in the code at the bottom of the first page is paid through the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923.

SOY INK

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue | Next Page

CMass

Next Page

## **Computer Highlights Society Magazines**

he IEEE Computer Society offers a lineup of 13 peer-reviewed technical magazines that cover cutting-edge topics in computing including scientific applications, design and test, security, Internet computing, machine intelligence, digital graphics, and computer history. Select articles from recent issues of Computer Society magazines are highlighted below.

### Söftware

More than 40 years ago, the term "software engineering" was coined as a challenge to establish software design and development on a firm engineering footing. Twenty years ago, Mary Shaw's classic article "Prospects for an Engineering Discipline of Software" assessed progress toward the establishment of software design and development on a firm engineering footing. Shaw's latest update, in the most recent *Software*, shows that the profession has made progress but still has much left to do.

### **Professional**

Ontologies represent items of knowledge—ideas, facts, things—in a way that defines the relationships and classifications of concepts within a specified domain of knowledge. It's this ability to define various useful relationships among items of knowledge, and to implement these relationships in software, that make an ontology such a powerful gadget in the knowledge manager's tool box. A new tutorial in *IT Pro*, "Just What Is an Ontology, Anyway?," by Thomas C. Jepsen, addresses several definitions of "ontology" as they relate to computer applications. Jepsen also gives an overview of common ontology-based applications.

#### Computer Graphics

Topics covered in *CG*&*A*'s special issue on recent developments in 3D user interface research include reality- and imagination-based interaction, pointing techniques, analysis of rapid aimed movements, temporal-data visualizations, and navigation of augmented CAD models.

### SECURITY PRIVACY

Virtually every Internet application relies on the Domain Name System, but security wasn't a major goal of its original design. The result is several critical vulnerabilities, reviewed in the September/October 2009 S & P special issue on DNS security. To address the security challenges, the security community developed DNS Security Extensions, which are undergoing deployment. Articles summarize key aspects of how to deploy DNSSEC at authoritative servers, resolvers, and public key learning.

### lntelligent Systems

E-government and e-participation research aims to provide technologies and tools for more efficient publicadministration systems and more participatory decision processes. To this end, interest is growing in how this challenging domain can benefit from emerging "intelligent" technologies, tools, and applications such as the Semantic Web, service-oriented architectures, Web 2.0, and social computing.

In "Transforming E-government and E-participation through IT," *IS* contributors Vassilios Peristeras, Gregoris Mentzas, Konstantinos A. Tarabanis, and Andreas Abecker note that governments invest heavily in information and communication technologies but are still far from satisfying their constituents.

## **Internet** Computing

Cloud computing is location agnostic and provides dynamically scalable and virtualized resources as services over the Internet. In a recent special issue of *IC*, the guest editors provide broad introductory definitions of

**4** COMPUTER

Published by the IEEE Computer Society

0018-9162/09/\$26.00 © 2009 IEEE

cloud computing concepts and introduce other articles that investigate some of the most fundamental issues concerning cloud services' development and deployment.

## 10

Photonic networks-on-chip have distinct advantages over electronic NoCs, including communication bandwidth approaching multiple terabits per second with limited power dissipation. In the July/August issue of Micro, Columbia University researchers explore the design of photonic NoCs for delivering a scalable solution to future multicore processors performance requirements in "Photonics NoCs: System-Level Design Exploration."

## **MultiMedia**

Steganography is the art and science of writing messages in a way that hides the existence of communication. It can be combined with cryptography to achieve a high level of security. Steganographic schemes abound for hiding messages in images with low dynamic ranges. However, these schemes operate in a fixed luminance range that doesn't work with images of high dynamic ranges, where each image has a different luminance range. An article in the July-September issue of MultiMedia, "A Novel Approach to Steganography in High-Dynamic-Range Images," presents a message-hiding approach for HDR images. The approach supports authentication and a large embedding capacity with low image distortion.

### Design&Test

The September/October D&T special issue on 3D IC integration is guest-edited by David Kung of IBM T.J. Watson Research Center and Yuan Xie of Pennsylvania State University. Four articles address different challenges to giving chip architects the flexibility and design options of 3D IC technology as they pursue solutions to the complexities and cost of scaling to 22 nm and beyond.

Nur Touba of the University of Texas at Austin, technical program chair for the 2008 International Test Conference, invited the authors of three outstanding conference papers to update their work for D & T.

## nnals

In Annals' July-September Anecdotes department, Stanley Mazor recollects his work as liaison to Magnavox in developing the Intel 8244 custom chip for Magnavox's Odyssey2 videogame console. Mazor teamed with Intel chip designer Peter Salmon to deliver the 8244 on time to meet Magnavox's announced plan to release the console by the 1977 holiday season. Intel met its schedule, although the Odyssey2 system didn't appear until 1979.

Mazor joined Intel in 1969. He worked with Ted Hoff and Federico Faggin to deliver the first working CPU, the Intel 4004, in 1971.

Editor: Bob Ward, Computer; bnward@computer.org

#### 5 **NOVEMBER 2009**

LETTERS

#### FORMAL VERSUS AGILE: AN OXYMORON

The article titled "Formal Versus Agile: Survival of the Fittest?" (S. Black et al., Sept. 2009, pp. 37-45) is at best an oxymoron.

Agile methods and formal methods have little in common. Or to put it simply: One size fits nobody, and agile fits very few.

Agile is good for very small projects and for throwaway code supporting research/experimentation. Formal methods should be used for any project that is nontrivial. The potential for useful overlap is miniscule.

The only place that agile fits, with a formal method, is at the front end of the *systems architecture* definition, where alternatives need to be explored. No amount of interchange will make people with *real* problems use agile methods except to support research about alternatives. And these days there is little that cannot be designed from real requirements without research that agile could actually be a help with. The exception may be to do drivers and test cases to evaluate hardware capabilities.

Nobody, at least nobody who is sane and rational, is going to give software folks a bunch of money just to see "what they can come up with." That is not to say that there are not PHBs who can get snookered by technobabble, but with the current economy, their numbers are being thinned down.

In the real world, real (functional) requirements are *required*, not optional. They are fixed; they do not change rapidly, if at all. They describe the essence of a solution to a problem. The best alternative solution will be further specified by derived requirements, which are subject to occasional change and constrained by nonfunctional requirements such as size, weight, power, security, reliability, and so on. It is unclear what problems change so fast that agile would be useful. "Requirements" that change are a sign that the real problem has not been defined and that a systems architecture has been bypassed to start design and development without knowing the framework that the "solution" should fit in.

Management has to work to a budget. They need products that are guaranteed to work and solve their problem. And they need them on time. Agile just does not do that in any but the simplest cases. *William Adams*

<u>williamadams@ieee.org</u>

#### The authors respond:

We thank William Adams for his comments. Unfortunately, his viewpoint seems to reflect the thinking of decades ago and is no longer appropriate. These days, agile is used very successfully on many large-scale projects and certainly not only for "very small projects and for throwaway code." For example, at the recent Agile 2008 Conference, Marcus Evans reported on the use of agile within the British Broadcasting Corporation (BBC) to develop the BBC iPlayer. The BBC iPlayer project has been described as a "project of the same importance as moving from B&W to color TV."

Another UK giant, British Telecommunications (BT), has used agile with great success. Indeed, according to Roger Leaton, agile advocate at BT, "Large-scale agile enablement, when done properly, really does work and transforms IT project delivery and business performance" ("How BT Learnt to Be Agile," 17 May 2008; www.computerworlduk.com/ toolbox/software-quality-testing/ quality-assurance/opinion/index. cfm?articleid=1416).

Regarding the comment that "Formal methods should be used for any project that is nontrivial," we are

proponents of formal methods, but would never agree with this statement. Formal methods have their place, as do agile and other development paradigms in the modern world of software engineering.

In our article, we set out to get colleagues thinking about the big picture regarding practical software engineering in the 21st century. We wanted to challenge stereotypical, old-fashioned thinking. We are happy that we have achieved that aim.

#### SAAS LIMITATIONS

In "The Web as the Ubiquitous Computer" (Web Technologies, V.S. Pendyala and S.S.Y. Shim, Sept. 2009, pp. 90-92), the authors provide information about software as a service (SaaS). Technological trends are clearly going in the direction of having applications online. Zero maintenance results in a lower total cost of ownership; hosted offerings are designed and finely tuned to scale seamlessly for large numbers of simultaneous users; and upgrades are made frequently and, for the customer, effortlessly.

However, there are several significant limitations that users must bear in mind before they select a hosted application. The sad truth is that computers can fail, resulting in service disruption, which has the potential to be catastrophic. Users are not only subject to network outages, they also must always be tethered to the Internet.

Sensitive data also may be vulnerable when hosted on someone else's server. In this case, users can't modify the software and they can't upgrade it. They are forced to accept changes that they might not even be aware of.

**6** COMPUTER

Computer

Published by the IEEE Computer Society

0018-9162/09/\$26.00 © 2009 IEEE

They lose control over what version of the software they are using. Although keeping up to date is one of the selling points for SaaS, in fact, too many new software versions may turn out to be problematic.

Computer

With SaaS, users keep paying. They can't own a license and use it freely. Whenever the SaaS provider changes its rates, users must pay the increased fee or risk losing access to their information.

The cost savings with SaaS is a huge benefit. However, it is important to realize that many of these cost savings could just be upfront costs associated with SaaS implementation. In the long run, it could be more expensive to maintain SaaS due to subscription costs.

If software systems are absolutely critical to a company's operation, a much better choice is to invest in a more reliable and comprehensive solution to support making guarantees to customers.

Hong-Lok Li <u>lihl@ams.ubc.ca</u>

#### The authors respond:

Points of failure cannot be avoided in any setup, including local environments. As described in the column, cloud environments tend to have better reliability and resilience intrinsic to large corporate setups. As we also stated, the Internet is now a household commodity and abundantly available. This is in fact a fundamental premise for the paradigm shift.

Vulnerability and losing control of data were covered in the column. It is not clear how that point applies to versioning, however. Irrespective of the environment, developers should always be in control of versioning their software. If the comment refers to versioning of the software on the leased servers, that is the case even with local servers. The users are bound by what the server vendor provides, whether deployed on a cloud or in the local environment. Vendors can discontinue support to older versions or include features in the new versions that the user may not like. In view of the economies of scale that the cloud provides, there is a greater likelihood of accessing better features.

This point about potential problems with the fee structure is covered in the "Challenges" section of the column. As mentioned there, users "could feel trapped and helpless when providers change their terms of service or operational methods after some time." Gains from economies of scale inherent in the cloud environment will help keep the costs down.

The new model is more likely to provide a reliable and comprehensive solution and make guarantees to customers than a homegrown environment. The investment and interest in this new model of computation itself is ample proof of this.

#### DEFINING COMPUTER ENGINEERING

Regarding "Defining Engineering" (Letters, Sept. 2009, p. 6-7): First, I contend that computer software development and programming has very little to do with mathematics. Computer software is a language solution to an automated world. A handyman with good communication skills will likely be as good at designing and developing software as an engineer who has memorized all the rules inside the box.

Many successful software developers have only modest ability in math—myself included—and so couldn't take a computer science degree in the average university because of the odious math prerequisites. So one of the most creative fields available is blocking many creative people because of the misperception that it requires math.

Second, when programmers are conceived of as technicians the

software architecture and design become brain-numbing bureaucratic functions; just produce the ambiguous diagrams and documents, argue about the document structure, get it all signed, and you're done. Oh, and ship it offshore for programming—it's already late.

Maybe the reason engineering can't come to grips with programming is that programming requires craft and abstraction as well as science, and that knowing all the minutiae of the theory may have little to do with effective practice. Too often, an "engineered" software application has many impressive features, but is maddeningly "unintuitive" to use. Doesn't engineering do "intuitive"? Even an airliner's complex instrument panel is designed for optimal usability by the user (the pilot). This doesn't just relate to screens and buttons-most levels of computer systems need to be understandable. Humans need to easily work on them, upgrade them, and interface with them without making errors of misunderstanding that cost time, money, and safety.

My education was in music and language, I have a BA, and I don't do math—but I have been a successful programmer (and now software architect) since 1972. My own programming experience includes data communications, finance, compiler development, psychomotor testing, animation, graphics, the Web, databases, diagnostic systems, user interfaces, and much else. I have software patents granted and pending, and I authored a successful college textbook on computer programming. *Harry Gilbert*

harrymgilbert@yahoo.com

We welcome your letters. Send them to <u>letters@computer.org</u>. Letters are subject to editing for style, clarity, and length.

#### NOVEMBER 2009

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue | Next Page

#### THE KNOWN WORLD

## Bad Alignment

David Alan Grier, George Washington University

Potential customers will be interested in new technology only if it somehow makes their lives better—if it moves them toward a goal they hold for themselves, their family, their company.

t wasn't working. Nothing was in alignment. The coffee was cold, the muffins were stale, and the software presentation was a forced march through a PowerPoint landscape denuded of life. Three hours had passed, and no civilization could be seen on the horizon. In command of the podium was a perky salesperson named Alena who led us through slide after slide with an inflection to her voice that suggested ideas of great magnitude where no new ideas could be heard. The eight of us on the committee sat in stone cold silence, praying that an all-merciful divine being would send a band of pirates to attack our meeting, seize this woman, and hold her hostage in a distant country.

We held no personal grudge against Alena. We could find no fault in her person or character. However, we could all see that the poor dear wasn't succeeding in the task assigned to her. As the representative of her employer, she was supposed to educate our committee and harmonize our aspirations with her company's goals, to show us that they would meet our needs when we met theirs. Such a task isn't easy, as it demands analysis, imagination, and more than a little empathy. These qualities aren't usually associated with pirates, but we were willing to take our chances. An open and unilateral statement of criminal assessment would have been far preferable to the presentation we were attending.

The problem of communicating the benefits of technology has bedeviled the industrial age from its inception. So often, new technology is conceived in terms of engineering specifications: processor speeds, data formats, power consumption, manufacturing costs. Rarely do potential customers see technology with the same eyes. They will be interested in new devices only if it somehow makes their lives better—if it moves them toward a goal they hold for themselves, their family, their company.

#### **PATTERSON'S SALES CYCLE**

As I watched the sales presentation, I could see that Alena had clearly been schooled in John Henry Patterson's sales cycle, though she probably knew little about the man.

Patterson was the president of the National Cash Register Company at the end of the 19th century. He was one of the first thinkers to understand the problem of explaining new technologies to nontechnical audiences. His novel technology, the cash register, was a marvel of mechanical engineering and attracted as much attention as the personal computer of a century later. Yet initially, that clever engineering—the high-precision gears, the multiple linkages, the novel bearing designs—wasn't sufficient to attract more than a few paying customers. When new customers were first introduced to the machine, with its engraved case and polished brass, they would usually react with the question, "What's in it for me?"

Patterson developed a four-step cycle for connecting the technology of cash registers with his customers' goals and drilled this cycle into his stales staff. The steps were easy to remember: identify and propose, demonstrate and close. They were much harder to follow.

The first step in the process required the salespeople to listen to their customers and discover their human needs. Did they feel that they were in control of their business? Were they earning enough to support their family? Were they spending too much time at their work? After identifying such issues, Patterson's salespeople were to propose ways that cash registers could be used to solve problems and then demonstrate those solutions. For

Computer

Published by the IEEE Computer Society

0018-9162/09/\$26.00 © 2009 IEEE

CMass

example, cash registers could reduce employee theft, simplify accounting, and track expenditures, which in turn would reduce anxiety, simplify labor, strengthen confldence.

The last step of the process, closure of the sale, brought the customer's goals in line with what National Cash Register had to offer. That was the most important part of the process for Patterson. "ABC," he told the National Cash Register representatives: "Always Be Closing."

#### **MISSING THE POINT**

Alena clearly understood the need to close a sale, but she didn't know how to work the other steps of the Patterson sales cycle. She started her presentation by saying that she wanted to listen to us and identify our needs, but she quickly proved that she was much more interested in identifying herself. In the course of 15 minutes, we learned about her academic credentials, the number of years she had worked for the company, the types of schools that had bought software from her, and, if memory serves correctly, the name of the Thai dressmaker who had created the suit she was wearing.

In telling her story, Alena was little different from the other salespeople who had appeared before us. As we listened to them, we had been regaled with corporate histories, stories of programmers who had developed their software, the revenue goals that had been met or exceeded by their regional office. Such stories were impressive at times but showed little analysis and less empathy.

Without identifying our needs, Alena and all the other salespeople had little to propose and less to demonstrate. They wandered through the remaining steps of the Patterson cycle like merchant ships lost on the stormy sea. They would tack toward one idea for a time before shifting to another in the hope that something might catch our attention. Eventually, they became lost and panicked. The flrst sign of trouble came when they started repeating the phrase, "The software will do whatever you want it to do."

The real evidence was seen in the acceleration of the PowerPoint slides. At the start of the presentation, they lingered for 30 or 40 seconds per slide. After the first hour, this dwell time dropped to 15 seconds or 20 at most. As we approached the third hour, slides were flashing on the screen for no more than 5 or 6 seconds.

The Shewhart cycle is the familiar fourstep process that shaped large parts of engineering practice: Plan. Do. Check. Analyze. Repeat.

These slides were detailed, technical graphics. Nested matrices. Symantec networks. Predicate calculus. Horn clauses. Each of these ideas fiew past our eyes accompanied by the plaintive cry, "whatever you want."

#### THE SHEWHART CYCLE

If Alena had asked me what I wanted to do, my response would have been unequivocal. I wanted to flnish my service on the committee as quickly as possible. While I could see an obvious strategy that would have aligned that goal with Alena's hopes, I had to acknowledge that the result wouldn't have been entirely satisfactory to all concerned. Our committee actually had a more noble goal: It had been assembled for the purpose of improving the university's approach to assessment.

In the world of academe, "assessment" is the term for the more prosaic concept of "quality control." Although it's based on ideas that are considerably older, it has been part of higher education for a little more than a decade. It uses educational analyses that were developed in the 1950s and employs a basic tool of quality control, the Shewhart cycle of continuous improvement, that dates to 1931.

The Shewhart cycle is the familiar four-step process that shaped large parts of engineering practice: Plan. Do. Check. Analyze. Repeat. "We like to believe that there is law and order in the world." Shewhart wrote. "We seek causal explanations of phenomena so that we may predict the nature of these same phenomena at any future time." He knew that sometimes natural phenomena could hide its operations, but he also had great faith in the analytic powers of the human mind. To support this faith, he liked to quote the poet of the English Enlightenment, Alexander Pope:

All Nature is but Art, unknown to thee; All chance, direction, which thou canst not see;

All discord, harmony not understood; All partial evil, universal good.

Yet, Shewhart didn't accept the mechanistic view of the universal good that was shared by Pope's 18thcentury contemporaries. He looked for universal good and hoped to flnd misapprehended harmonies, but knew that analytic reason couldn't always flnd them. We "are limited in doing what we want to do," Shewhart explained, because understanding every aspect of even a simple manufacturing task in its entirety "requires almost infinite knowledge." Therefore, quality control required the good engineer to "accept as axiomatic that we cannot do what we want to do and cannot hope to understand why we cannot "

#### **AT&T STRATEGY**

Shewhart developed his cycle in conjunction with a statistical methodology that allowed engineers to search for problems in production and flnd ways of bringing those problems under control, at least for a short

NOVEMBER 2009

#### THE KNOWN WORLD

time. This method was well suited for Shewhart's employer, the American Telephone and Telegraph Company (AT&T), because it was a highly complicated business that followed a simple, well-articulated goal: universal service.

When AT&T began expanding in the early 20th century, its leadership concluded that both its customers and investors would be best served by a company that offered a standard telephone service across the US and could dominate every market in which it operated. This goal required a uniformity beyond the scope of the accomplishments of any company operating at that time. Yet, management argued that its goals required "standardized operating methods, plant facilities and equipment," explained an early company president, and also "complete harmony and cooperation of operating forces through centralized and common control"

AT&T's common goal simplified the human dynamics of quality control, making it easier for a team of engineers to empathize with the needs of their neighbor. As would any team of engineers, marching through the steps of plan, do, check, and analyze, they would need to understand how other units might view their proposal, which in turn required them to imagine how these units approached the goal of universal service. Of course, such a goal didn't eliminate differences within the corporation, as all employees would interpret universal service in light of their own opinions and aspirations. However, it gave a much stronger foundation for resolving disagreements than the goals found at most universities.

## EVALUATING ENGINEERING EDUCATION

In words that have often been expanded and embellished, a university president once described the modern institution of higher education as a collection of rival, warring tribal factions united by a common heating system. Lacking a common heating system, our school was united by complaints about the parking lots. As most of the members of the assessment committee took public transportation, we were barely united at all.

In spite of our discontent, some of our committee members were comfortable with the academic ideas of quality control and even with the presentations by the software sales

The committee established the idea that education could be studied with the tools of engineering and that education needed to be treated as a process that requires continuous improvement.

teams. In particular, the engineers saw how they might employ these pieces of software as they had the longest history with educational assessment. Engineering faculty began developing the concepts of educational quality control at roughly the same time that Shewhart developed his methods for AT&T.

In 1929, the Carnegie Foundation for Teaching established a committee to investigate the state of engineering education. To chair the committee, they recruited William Wickenden, who had been a senior manager at AT&T and was then president of the Case School of Applied Science in Cleveland. Wickenden created an extraordinarily detailed plan for his committee. A preliminary plan shows subdivisions of authority, lines of communication, data flows, and responsibility for outcomes. He had grand designs for the committee, "a comprehensive survey of the whole situation—students and graduates, faculty and facilities, curricula and methods, professional engineers and industry, and the economic and social significance of engineering."

In the end, Wickenden's committee produced a sympathetic report. Well before they completed their work, the members concluded that "there were no glaring defects in the contemporaneous policies and methods of engineering education." At the same time, the committee established the idea that education could be studied with the tools of engineering and that education needed to be treated as a process that requires continuous improvement. "There were many readjustments which were needed," the committee concluded. "The situation called not for revolution but evolution." It was a call to apply the ideas of Walter Shewhart: Plan. Do. Check. Analyze. Repeat.

#### **DIFFERING VIEWPOINTS**

I don't know if Alena and her team did a formal assessment of their presentation to our committee. If they did, the feedback for their Shewhart cycle would have been swift, brutal, and obvious. We didn't buy their software. If they looked more deeply at our response, they might have discovered that the members of the committee responded in different ways to their presentation. The variations in these responses were determined not only by the different goals of each school, but also by the social structure in which each school operates.

The engineering school, by far the most sympathetic to Alena and her colleagues, is part of a complicated but unified social structure. This structure contains accrediting bodies, engineering societies, and professional exam boards. These groups are used to debating the nature of education and flnding common ground among themselves.

By contrast, the College of Policy and Current Events abides in an

**Q**Mags

anarchistic landscape and has little experience in working with other institutions to define the goals of higher education. The combative nature of the group is suggested by the titles of its courses: Civil Wars, Terrorism, Military Strategy. It even teaches classes in pirate theory, though we tend to call such courses "Transnational Security Threats" and limit the examples to the modern pirates of Sudan and the Strait of Malacca.

ccording to the best scholars of the fleld, pirates are most effective when they can control their operational goals, when they can build a strong bond of empathy

among their band. To do this, they usually need the tacit approval of a nation-state, freedom from absent owners (usually achieved by stealing a boat or buying one with stolen funds), and assembling a team that accepts the twin goals of expanding plunder and avoiding capture. The situation doesn't quite parallel the AT&T of the 1930s with its goal of universal service, but it works tolerably well. In this circumstance, they have a simple debate over Shewhart's cycle. Will a new strategy increase the chances of gaining treasure? Will it make them more vulnerable to naval attack? They usually demand a full discussion of all hopes and doubts in such debates.

No pirate wants to worry about the concerns of others in the midst of a raid. Perhaps because of this, they are never available when you need them to disrupt a sales presentation that has gone badly out of alignment.

Mass

David Alan Grier, the author of Too Soon to Tell (IEEE CS Press, 2009), is an associate professor at the George Washington University, where he teaches science and technology policy and leaves the theory of piracy to others. Contact him at grier@gwu. edu.

CN Selected CS articles and columns are available for free at http://ComputingNow.computer.org.

# <sup>••</sup>All writers are vain, selfish and lazy.

—George Orwell, "Why I Write" (1947)

## (except ours!)

The IEEE Computer Society Press is currently seeking authors. The CS Press publishes, promotes, and distributes a wide variety of authoritative computer science and engineering texts. It offers authors the prestige of the IEEE Computer Society imprint, combined with the worldwide sales and marketing power of our partner, the international scientific and technical publisher Wiley & Sons.

For more information contact Kate Guillemette, Product Development Editor, at kguillemette@computer.org.

www.computer.org/cspress

**NOVEMBER 2009**

11

32 & 16 YEARS AGO

#### **NOVEMBER 1977**

**COMPUTER NETWORKS** (p. 11) "Networks of computers are making it possible to achieve computer-to-computer and terminal-to-computer communications that only a few years ago would have been impossible. Many of these networks are operational already, with more powerful ones seemingly in store for the future. This remarkable growth has opened new opportunities for designers, users, and managers—but it has posed some difficult problems for them as well. Knowledge of such network issues as topological design alternatives, common carrier communications services, value-added networks, hardware and software networking technology, cost factors, regulatory issues, measurement techniques, and network administration are of paramount importance."

NETWORK COMPLEXITY (p. 12) "The complexity of computer networks has taken a dramatic upswing, following significant developments in electronic technology such as medium- and large-scale integrated circuits and microprocessors. Along with this upswing in complexity, several sophisticated network classification schemes have evolved. Abstruse terminology-such as centralized, circuit switching, deterministic, distributed, packet switching, and stochastic-frequently appears in discussions and papers, to an extent that often confuses communication subnet users. For example, how many readers would immediately recognize that centralized networks inherently have a deterministic routing policy? or know whether or not distributed networks are necessarily packet switching networks, or may instead be message switching?"

SERVICE MEASUREMENT (p. 32) "Suitable measures for the comparison of computer services have been discussed in detail by Abrams and Treu, who identified more than 50 possible measures of the computer service delivered through a remote terminal, on the basis of time, lengths, rates, and ratios. Further, sophisticated hardware and software tools in the form of mechanized measurement drivers have been developed to collect performance measurements from the systems under study. The comparison methodology, however, is currently lacking an appropriate experimental design which will provide, with a specified level of confidence, the answer to the question of real interest: Which system is the best?"

NETWORK AVAILABILITY (p. 43) "The principal opportunity for increasing the availability of a network of computers results from the presence of multiple, reasonably autonomous processors. First, when a software failure does occur which disables a node of the network, and the malfunction can be confined to that node, the network may continue to provide at least some level of service to some of its users. The network may even continue operation so as to make the failure transparent to nearly all users. On the other hand, if all service were being provided by a single central computer, an

unrecoverable failure in the operating system running on the one CPU would interrupt service to all users until the system could be restarted."

Next Page

ROUTING (p. 60) "There are basically two different types of system control procedures. An open-loop control system is one in which system control actions are taken in a prespecified manner that is independent of both current system state and past response. Open-loop control laws are usually simple in form but are practically useful only in those systems where the evolution of system response can be accurately predicted from given data. A closed-loop control system is one in which control action depends on current system state and possibly also on dynamic response history. Closed-loop systems are usually characterized by a relative insensitivity to parameter variations, and they are flexible enough to control system response successfully even in the presence of unpredictable system inputs. The design of closed-loop systems is frequently difficult because of the related problems of stability, accuracy, and speed of response."

**PRODUCTIVITY AND COMPUTERS** (p. 66) "The computer is a vital factor in productivity improvement. Economic research by Edward Dennison and others indicates that almost half of the US increase in productivity is attributable to technological innovation. Since computers represent one of the most important technological advances of the 20th century, as well as being a factor in the other major sources of productivity gains, we can conservatively estimate that computer usage has provided at least 15% of the 2% growth in productivity for the last decade, or 0.3 percentage point."

JOBS AND PEOPLE (p. 87) "On-the-spot matching of jobs to people as well as people to jobs, using real-time computer techniques, is now an everyday routine at seven job centers run by the Employment Service Agency in London. The computer system, which the ESA claims leads the rest of the world and is arousing interest in the U.S. as well as Europe, began live operation at the Romford job center in March."

12 COMPUTER

Published by the IEEE Computer Society

0018-9162/09/\$26.00 © 2009 IEEE

#### **NOVEMBER 1993**

PARALLELISM (p. 20) "Today's workstations have redefined the way the computing community distributes processing resources, and tomorrow's machines will continue this trend with higher bandwidth networks and higher computational performance. One way to obtain higher computational performance is to use special parallel coprocessors to perform functions such as motion and color support of high-definition screens. Future computationally intensive applications suited for desktop computing machines include real-time text, speech, and image processing. These applications require massive parallelism."

SYSTEMS ENGINEERING (p. 54) "Developing large computer-based systems with complex dynamics and component interdependencies requires analysis of critical end-to-end processing flows to determine feasibility and proper allocation. Currently, no engineering discipline provides the knowledge base for the necessary trade-off studies concerning software, hardware, and communication components; a new discipline is needed at the systems engineering level.

"Industry has recognized the size and scope of problems with systems engineering processes, and several organizations have been formed to advance the systems engineering discipline. || However, recognition of the need for a special discipline addressing the system engineering of computer-based systems (ECBS) is just emerging, as evidenced by the recently formed IEEE Computer Society Task Force on ECBS and recently published textbooks."

JOHN BACKUS (p. 78) "John Backus has been named recipient of the 1993 Charles Stark Draper Prize, the highest honor of the National Academy of Engineering (NAE). The award, which carries a \$375,000 stipend and a gold medal, is the largest prize in engineering, according to the NAE.

"Backus was cited for the development of Fortran-the first general-purpose, high-level computer languagewhich ushered in the computer software revolution and a \$23 billion industry. 'Before John Backus, only a handful of specialists could use the computer,' said Robert M. White, NAE president. 'Today, everyone from preschoolers to postgraduates can use the computer."

SPEECH TRANSLATION (p. 78) "A computer scientist specializing in artificial intelligence is bypassing traditional AI methods in an effort to improve the performance of speechto-speech translation. So far he has achieved a 75 percent accuracy rate when testing his program on 1,600 sentences."

"[Hiroaki] Kitano, once a professional simultaneous interpreter, envisions a world in which hand-held computers will enable native and foreign speakers to converse anywhere."

**DIGITAL LIBRARIES** (p. 79) "The hypertext industry predicted by [Vannevar] Bush in 1945 emerged slowly, however. It was only in the late 1980s, years after Ted Nelson's vision of Xanadu, Brown University's IRIS (Institute for Research in Information and Scholarship) Project, and many other development efforts (Apple's Hyper-Card, for example) that this field came into international prominence. Yet hypertext still awaits the broader commercialization that will result from further R&D and technology transfer."

THE POSIX STANDARD (p. 81) "Through its efforts to develop standard interfaces for portable operating systems and publication of the Posix standard, the IEEE Computer Society has provided a dynamic environment for observing the changing role of testing in an open-systems environment. Clearly, the ability to achieve goals such as portability and interoperability is directly related to the ability to enforce adherence to a standard.

"Less obvious is the impact of developing standards and test methods concurrently. The generation of test methods during standard development promotes higher quality standards by providing immediate feedback to the standards development process. As the development process matures, lessons learned through experiences such as Posix will likely demonstrate that both these roles of enforcing adherence to the standard and improving its quality are crucial to its success."

APPLE'S NEWTON (p. 104) "With [John] Sculley's ouster-Apple didn't call it that mind you, but Silicon Valley insiders insist that he was squeezed out-Apple not only appears to be taking the conservative route vis-a-vis their once premiere visionary, but also the man who was responsible for the next generation of data management: the Newton. This palm-sized computer/fax machine/cellular telephone has the potential to virtually upend not only computing, but also the entire industry of personal communications. Unfortunately, without Sculley, the Newton loses its only advocate possessing the power and influence to ensure adequate allocation of further research and development funding. Without that funding, the Newton stands a poor chance of ever reaching its true potential."

PDFs of the articles and departments from the November 1977 and 1993 issues of Computer are available through the IEEE Computer Society's website: www.computer.org/ computer.

Editor: Neville Holmes; neville.holmes@utas.edu.au

0018-9162/09/\$26.00 © 2009 IEEE

Published by the IEEE Computer Society

13 **NOVEMBER 2009**

Mass

CMags

## There's no such thing as science fiction. Just stuff we haven't made yet.

From 20,000 feet under the sea to the dark side of the moon, and everywhere in between, you'll find the work of IEEE members. It's in a thousand things our founders could only dream of in 1884.

In fact, IEEE members have taken the stuff of science fiction and made it part of every day life. That's why, whether you need to draw on the knowledge of technology's past pioneers or today's innovators, one fact is clear—you'll see that IEEE members aren't just waiting for the future, they're engineering it—and the best chapte<u>rs are yet to come</u>.

#### Celebrating 125 Years of Engineering the Future

#### **TECHNOLOGY NEWS**

## Anonymization Technology Takes a High Profile

Neal Leavitt

Next Page

Increasingly, governments and various types of organizations are trying to either block or track Internet access and online communications by dissidents, employees, or others. To sidestep these activities, users are turning to anonymization technology.

Previous Page | Contents | Zoom in | Zoom out | Front Cover | Search Issue |

ensorship and the increased tracking of users online have become important topics. Numerous governments censor computer- and network-based communications to keep their citizens from freely getting news from or transmitting information to the outside world.

Dissidents and everyday Internet users—as well as criminals and others who want their online identities to be secret—have turned to anonymization technology to keep from being identified. This has made the technology more important and widely used in recent years, sparking the start up of anonymization companies and the development of new techniques.

"The evolving threats, the introduction of new technologies and applications, and the emergence of Internet censorship are really driving [the approach] right now," said Lance Cottrell, the founder and chief scientist of anonymization vendor Anonymizer. "And events like the recent elections in Iran have really drawn attention to it." In Iran, protesters against the results of the recent presidential elections fought government censorship to communicate with the outside world.

Anonymization technology faces numerous challenges to increased adoption and commercial success. Moreover, the technology has generated controversy among those concerned that terrorists, pedophiles, criminals, and others could take advantage of it.

#### **THE BASICS**

Anonymity systems prevent observers from discovering the source of online communications. Typically, the system keeps a recipient or observer of a transmission from seeing the IP address of a source or tracking a message back to its originator.

"The name of the game is to keep the servers you visit from knowing your IP address, which means not connecting to them directly. This means going through one or more other computers [called *proxies*] to arrive at the desired destination," said James Marshall, an independent consultant and software developer who created CGIProxy, a free Web proxy. Some anonymity systems also encrypt data.

#### History

The first popular anonymization tool was the Penet remailer developed by Johan Helsingius of Finland in the early 1990s. Penet was not totally safe for users because it kept a potentially accessible record of their names.

Some members of the Cypherpunk privacy and cryptography developers' group released their eponymous remailer in 1992.

Cottrell wrote the Mixmaster remailer in 1993. In 1995, he launched Anonymizer—the first Web-based anonymity system, initially a free service but now a commercial product.

#### **Driving forces**

Concerns about communications privacy are driving anonymization technology's increased adoption.

And as Internet use has grown, criminals have increasingly gone online to break the law, noted Rob Enderle, principal analyst with the

0018-9162/09/\$26.00 © 2009 IEEE

Computer

Published by the IEEE Computer Society

**TECHNOLOGY NEWS**

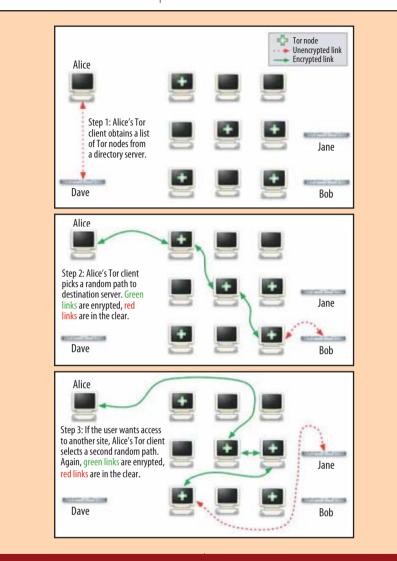

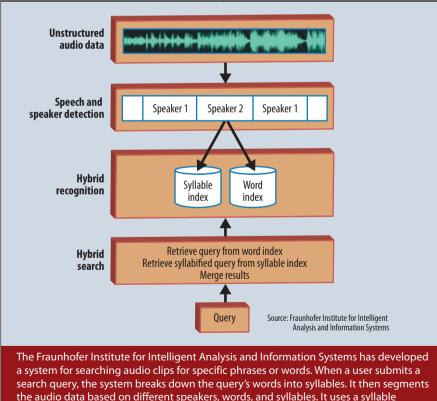

Figure 1. The Tor anonymization system hides a user's identity by sending traffic through a series of participating nodes.

Enderle Group, a market research firm. In the process, they have looked for ways to keep law-enforcement agencies from identifying them.

In some countries, libraries and employers block content, and some ISPs and websites record people's Web habits for marketing purposes.

Dissidents and other protesters also want ways to communicate without governments being able to identify or trace transmissions back to them.

The 2006 OpenNet Initiative (<u>http://opennet.net</u>)—a research project by Harvard University and the Universities of Cambridge, Oxford, and Toronto—studied Internet censorship and surveillance in 46 countries. The study found that 25 of the nations filtered various types of communications—including political content, religious sites, and pornography—by blocking transmission to and, in some cases, from specific IP addresses.

Officials identify sources they want to block by tracking back communications and identifying their senders via tools such as traceroute and services such as whois. They also find sites to block by using search engines and monitoring discussion groups and chat rooms. Some individuals and organizations identify various sources' IP addresses and sell the information to governments or other interested parties. lass

#### **UNDER THE HOOD**

Over time, demand for anonymization has grown and the types of uses, applications, and business models have evolved.

*Commercial anonymization systems*, such as SwissVPN (<u>www</u>. <u>swissvpn.net</u>), charge subscription fees for their services.

Noncommercial anonymization systems don't charge fees but instead generate revenue by selling advertising that appears on their webpages.

Home-brewed anonymization systems are based on anonymizing proxy packages, such as CGIProxy and Freenet, available online for free. They are popular with college students who use them to circumvent school networks' URL filtering systems.

#### **Types of anonymizers**

Users can install software to implement *simple virtual private network (VPN) systems*, such as Anonymizer Total Net Shield and Perfect Privacy. VPNs create encrypted tunnels through which traffic passes. Recipients or observers cannot read the encrypted traffic and thus cannot track it back to the sender.

Users can also install software for *simple proxies*, also known as *open proxies* and *anonymous proxies*. Users enter the proxy's IP address or hostname in their browser's network settings, and when they point their browser at a website, the browser tells the proxy which site to visit. The proxy visits the site on the users' behalf and sends the content back to them.

The systems remove the users' IP information from packets and replace it with their own IP information, said Rolf Wendolsky, a director of anonymization vendor JonDos.

The typical proxy provider sets up a server on the Internet through

C Mags

which users can relay traffic, which some anonymization applications encrypt. This *single-hop architecture* is easy to implement and maintain. However, users all enter and leave through the same server, thereby creating a single point of failure.

Daisy-chaining anonymization, which uses a *multihop* approach, sends a user's traffic through a series of participating nodes, as Figure 1 shows. The traffic travels a path which either the user or the anonymization software selects, depending on the application. The goal is to route traffic through nodes owned by different individuals or organizations. That way, no one organization can see enough packet information to identify the user.

With *form-based proxies*—such as Anonymizer Anonymous Surfing and Anonymouse—users enter the URL of websites they want to visit into a form field on an anonymization provider's page. The provider then takes the user to the desired site. The anonymization software rewrites links on the delivered page so that they connect to the provider, preventing anyone from tracing the transaction back to the original user.

Form-based proxies are written via either common-gateway-interface scripts, designed to transfer information from forms and other online sources between a Web server and a browser; or PHP Hypertext Preprocessor scripts, which run on a Web server and enable dynamic Web content such as forms.

Form-based proxies are popular because users don't have to configure or install any software.

However, they are the most insecure of all anonymization systems, said Wendolsky. For example, attacks could use form-based proxies to replace links on websites with URLs that send users to malicious sites.

"The disadvantage of such systems is [slower] performance, both because of the multiple hops and because of the poor performance of many nodes," explained Cottrell. Also, he added, users can't always judge the trustworthiness of the participating nodes' owners.

#### **Protocol support**

Protocol-specific systems like Anonymouse and PHProxy anonymize online activities—for example, e-mail or Web access—based on only one or several application-layer protocols, such as HTTP or the Simple Mail Transfer Protocol, thus they are not versatile. ments and user payments, open, protocol-specific

- I2P (Invisible Internet Project, <u>www.i2p2.de)</u>: VPN system, free, closed to all but those on subscribing networks, open source, protocol-independent, encrypts communications

- JonDonym (<u>https://www.jondos.</u> <u>de/en</u>): multihop proxy system; free and commercial versions; open source; open; encrypts communications; originally developed by the Technical Uni-

## Anonymization technology faces numerous challenges to increased adoption and commercial success.

But because they are designed to work in detail with only certain types of applications, they can effectively recognize and strip out all user-specific data from the traffic they send.

Protocol-independent systems such as JonDonym use approaches such as SOCKS—designed to send TCP traffic via a proxy server—which supports many communications protocols. They can also take advantage of VPNs, which also work with many protocols.

Although these systems obscure the path that traffic takes, they don't generally "understand" traffic well enough to actually change data in packets, which could reduce their effectiveness.

#### **APPLICATIONS**

The leading anonymizing applications include the following:

- Anonymizer (www.anonymizer. com): VPN- and form-based systems, supported by user payments, open to anyone on the Internet, protocol-independent, encrypts communications

- Anonymouse (<u>http://anony-mouse.org</u>): form-based system, supported by on-site advertise-

versity of Dresden, the University of Regensburg, and JonDos

- Megaproxy (www.megaproxy. com): VPN system, supported by user payments, open, protocol-independent, encrypts communications

- Proxify (<u>http://proxify.com</u>): form-based proxy system, supported by advertisements or user payments, protocol-independent, encrypts communications

- Tor (www.torproject.org): multihop proxy system; free; open; open source; protocol-independent; encrypts communications; started in 2003 with 30 proxies on two continents, now has 2,000 on five continents and up to 500,000 users at any one time

- XeroBank (https://xerobank. <u>com</u>): multihop-proxy and VPN systems, supported by user payments, partially open source, open, protocol-independent, encrypts communications

#### CHALLENGES AND CONTROVERSY

Criminals could take advantage of improved anonymization technology to hide their identities, said analyst Enderle.

#### NOVEMBER 2009 17

#### **TECHNOLOGY NEWS**

Also, anonymizers aren't foolproof. For example, if the first and last proxies in a system are malicious or compromised, the first proxy would know the client's identity and the last proxy would know the server's identity, explained Indiana University assistant professor Apu Kapadia. If the same person owns both proxies or if their separate owners communicate, this could break anonymity, he said.

Most open source projects publish enough information about their workings, including node addresses, to let governments or other organizations block traffic from at least some of those nodes, noted Cottrell.

According to Seth Schoen, staff technologist for the Electronic Frontier Foundation, a privacy and Internet-user-rights organization, there is a risk that some single-proxy anonymizer services may log users' IP addresses. If governments order them to turn over information or hackers break into their servers, users could lose their anonymity, he explained.

However, he noted, providing greater security would hurt performance because additional proxies and encryption increase overhead.

In fact, performance overhead sometimes causes anonymization to slow users' Internet access.

Expanding the number of nodes in anonymization systems could be difficult because users serving as nodes will experience a lot of traffic flowing through their computers.

Some ISPs block nodes to control spam. If, in the process, they block those used by anonymizers, Marshall said, this would hurt anonymization.

Browser complexity and the need to maintain browsing functionality could help proficient hackers sidestep anonymization, noted Wendolsky. Hackers could accomplish this in some cases, he explained, by exploit-

ing browser plug-ins, JavaScript, cookies, caches, or HTML parsing engines.

nalyst Enderle stated, "Anonymizers are wrongheaded." The technology conceals identities, he said, which makes it attractive to criminals.

The technology's two biggest marketplace challenges are cultural and legal, according to Cottrell. "The legal challenge is that some countries are outlawing or could decide to prohibit the use of privacy tools and require all Internet providers to keep detailed access records. The cultural issue is the trend toward [openness on the Internet]."

However, proponents say that privacy and the desire to communicate online without fear of identification or government retribution are among the good reasons to use anonymization and that this will drive the technology's continued development and adoption.

Anonymizer, for example, has reported a 20 percent annual growth in its business over the past few years.

Marshall predicted that anonymization will have a bright future, with more organizations developing systems as people become aware of its importance. He said, "The demand is there."

Neal Leavitt is president of Leavitt Communications (<u>www.leavcom.</u> <u>com</u>), a Fallbrook, California-based international marketing communications company with affiliate offices in Brazil, France, Germany, Hong Kong, India, and the UK. He writes frequently on technology topics and can be reached at neal@leavcom.com.

Editor: Lee Garber, Computer, I.garber@computer.org

**q**Mags

| <u>Organizing Committee</u><br>Chair:                        | IEEE Symp                                                                        |

|--------------------------------------------------------------|----------------------------------------------------------------------------------|

| <b>T. Nakamura</b> Keio Univ.                                | A A A A A A A A A A A A A A A A A A A                                            |

| Vice Chairs:                                                 |                                                                                  |

| Y. Hagiwara Sojo Univ./AIPS                                  | Yokohan                                                                          |

| H. Kobayashi Tohoku Univ.<br>J. Torrellas Univ. of Illinois, | (Yokohama Med                                                                    |

| Urbana-Champaign                                             |                                                                                  |

| K. Uchiyama Hitachi                                          | 2-1 10                                                                           |

| CM. Kyung KAIST                                              | CA                                                                               |

| Secretary:                                                   | COOL Chips is an Internat                                                        |

| K. Suzuki NEC Electronics<br>Treasurers:                     | power and high-speed chip                                                        |

| <b>T. Ogura</b> Ritsumeikan Univ.                            | microprocessors and their                                                        |

| H. Iwasaki NTT                                               | April 14-16, 2010, and is ta                                                     |

| Program Chairs:                                              | special emphasis on the area                                                     |

| M. Ikeda Univ. of Tokyo                                      | MICRO to publish selected                                                        |

| F. Arakawa Renesas Tech.                                     | <u>Contribu</u>                                                                  |

| Publicity Chairs:<br>M. Suzuki Panasonic                     | <ul> <li>Low Power-High Perfor</li> </ul>                                        |

| M. Nishihara IBM                                             | Multimedia, Digital Co                                                           |

| Publication Chairs:                                          | Automotive, Networkir                                                            |

| Y. Unekawa Toshiba                                           | <ul> <li>Novel Architectures and</li> </ul>                                      |

| Y. Hirose Fujitsu Labs.                                      | Single Core, Multi-Cor                                                           |

| Registration Chairs:<br>Y. Mori Oki Network LSI              | Ubiquitous, Dependabl                                                            |

| <b>R. Egawa</b> Tohoku Univ.                                 | <ul> <li>Cool Software including</li> </ul>                                      |

| Local Arrangement Chairs:                                    | Binary Translations, C                                                           |

| Y. Nitta Renesas Tech.                                       | Proposals should consist of                                                      |

| A. Hashiguchi Sony                                           | topic to be presented and the                                                    |

| Web Manager:<br>Y. Sato JAIST                                | address of the presenter. T                                                      |

|                                                              | this is a not-yet-announced please indicate it. We will d                        |

| Advisory Committee                                           | the program committee's ev                                                       |

| Chair:                                                       | e-mail, (Author's kit can be                                                     |

| M. J. Flynn Stanford Univ.                                   | to: Makoto Ikeda, Program                                                        |

| V <b>ice Chair:</b><br>T. L. Kunii Kanazawa                  | Author Schedule: Janua                                                           |

| Inst. of Tech.                                               | March                                                                            |

| Members:                                                     | March                                                                            |

| <b>D. Allison</b> Stanford Univ.                             | You are also invited to subn<br>to : M. Muroyama, Poster C                       |

| <b>D. B. Alpert</b> Camelback                                | Author Schedule: March                                                           |

| Computer Architecture A. J. Baum Intel                       | March                                                                            |

| <b>D. A. Draper</b> True Circuits                            | For more information, pleas                                                      |

| (TCMCOMP Chair)                                              | For any questions, please co                                                     |

| M. A. Franklin Washington Univ.                              | Sponsored by the Technical Committee                                             |

| G. Goto Yamagata Univ.                                       | Society. In cooperation with the IEIC                                            |

| M. Hase NTT<br>S. Hijiya Fujitsu Labs.                       |                                                                                  |

| <b>S. Iwade</b> Osaka Inst. of Tech.                         | ¥. (                                                                             |

| L. Jow Hewlett-Packard                                       | Celebrating 125 Years<br>of Engineering the Future                               |

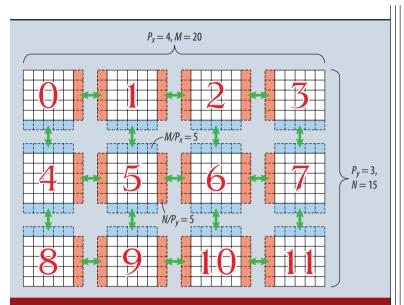

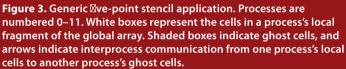

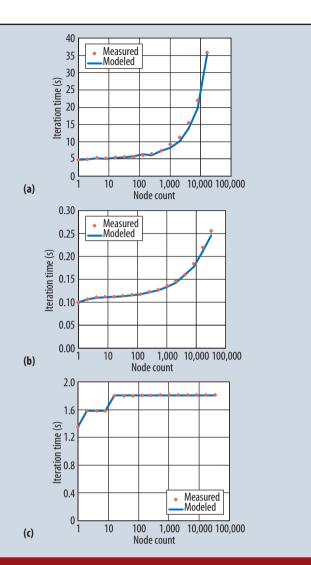

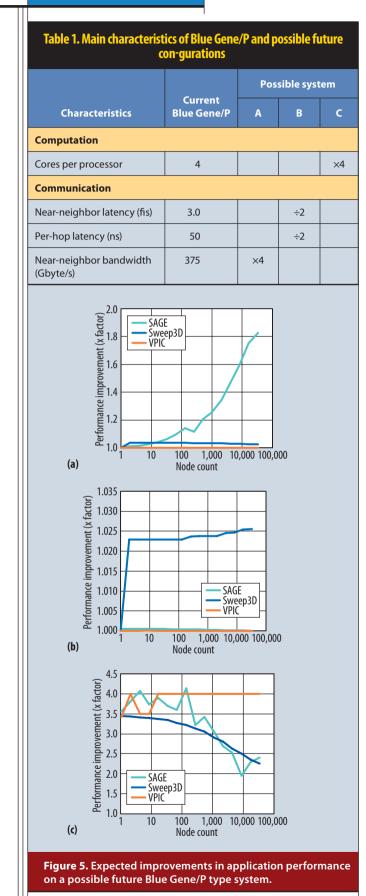

| R. Kasai NTT Electronics                                     |                                                                                  |